RM0090 System configuration controller (SYSCFG)

Doc ID 018909 Rev 4 208/1422

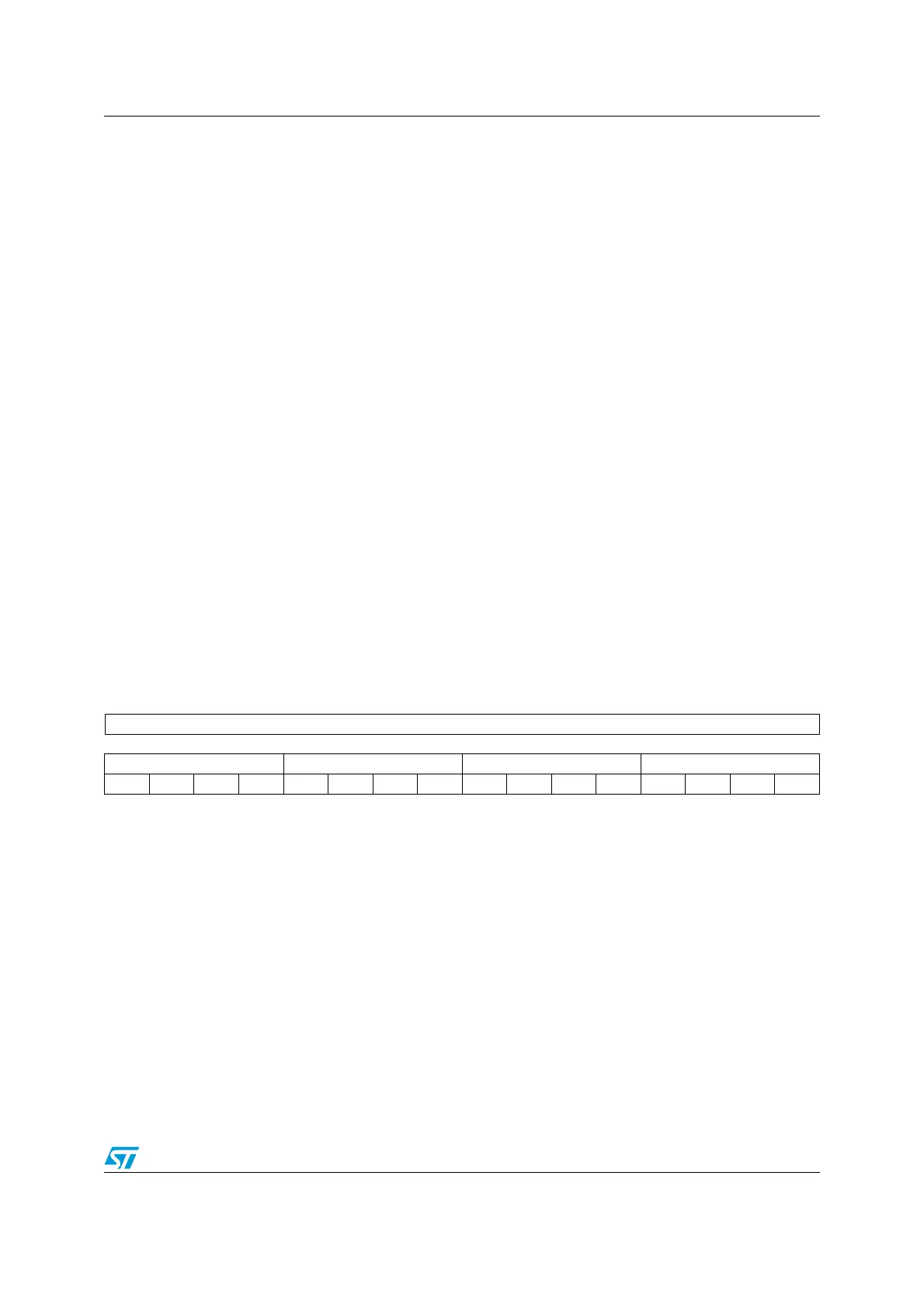

8.2.4 SYSCFG external interrupt configuration register 1

(SYSCFG_EXTICR1)

Address offset: 0x08

Reset value: 0x0000

Bits 31:24 Reserved, must be kept at reset value.

Bit 23 MII_RMII_SEL: Ethernet PHY interface selection

Set and Cleared by software.These bits control the PHY interface for the

Ethernet MAC.

0: MII interface is selected

1: RMII Why interface is selected

Note: This configuration must be done while the MAC is under reset and before

enabling the MAC clocks.

Bits 22:19 Reserved, must be kept at reset value.

Bits 18:16 ADCxDC2:

0: No effect.

1: Refer to AN4073 on how to use this bit .

Note: These bits can be set only if the following conditions are met:

- ADC clock higher or equal to 30 MHz.

- Only one ADCxDC2 bit must be selected if ADC conversions do not start

at the same time and the sampling times differ.

- These bits must not be set when the ADCDC1 bit is set in PWR_CR

register.

Bits 15:0 Reserved, must be kept at reset value.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

EXTI3[3:0] EXTI2[3:0] EXTI1[3:0] EXTI0[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 EXTIx[3:0]: EXTI x configuration (x = 0 to 3)

These bits are written by software to select the source input for the EXTIx

external interrupt.

0000: PA[x] pin

0001: PB[x] pin

0010: PC[x] pin

0011: PD[x] pin

0100: PE[x] pin

0101: PF[C] pin

0110: PG[x] pin

0111: PH[x] pin

1000: PI[x] pin

Loading...

Loading...