RM0090 Secure digital input/output interface (SDIO)

Doc ID 018909 Rev 4 850/1422

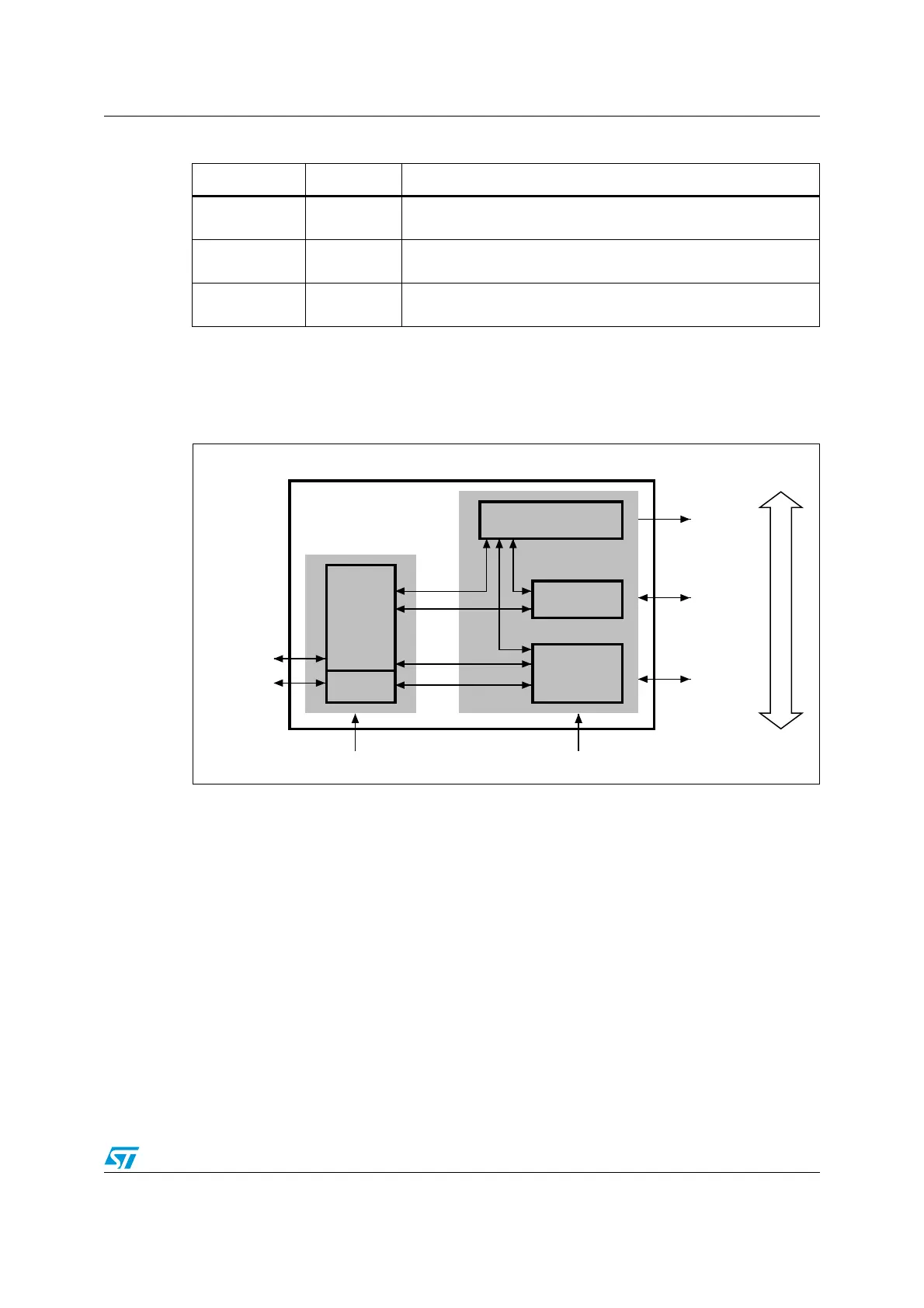

28.3.1 SDIO adapter

Figure 314 shows a simplified block diagram of an SDIO adapter.

Figure 314. SDIO adapter

The SDIO adapter is a multimedia/secure digital memory card bus master that provides an

interface to a multimedia card stack or to a secure digital memory card. It consists of five

subunits:

● Adapter register block

● Control unit

● Command path

● Data path

● Data FIFO

Note: The adapter registers and FIFO use the APB2 bus clock domain (PCLK2). The control unit,

command path and data path use the SDIO adapter clock domain (SDIOCLK).

Adapter register block

The adapter register block contains all system registers. This block also generates the

signals that clear the static flags in the multimedia card. The clear signals are generated

when 1 is written into the corresponding bit location in the SDIO Clear register.

Table 128. SDIO I/O definitions

Pin Direction Description

SDIO_CK Output

MultiMediaCard/SD/SDIO card clock. This pin is the clock from

host to card.

SDIO_CMD Bidirectional

MultiMediaCard/SD/SDIO card command. This pin is the

bidirectional command/response signal.

SDIO_D[7:0] Bidirectional

MultiMediaCard/SD/SDIO card data. These pins are the

bidirectional databus.

ai15899

Control unit

Command

path

Data path

Adapter

registers

FIFO

SDIO_CK

SDIO_CMD

SDIO_D[7:0]

PCLK2 SDIOCLK

Card bus

SDIO adapter

Loading...

Loading...