Cryptographic processor (CRYP) RM0090

579/1422 Doc ID 018909 Rev 4

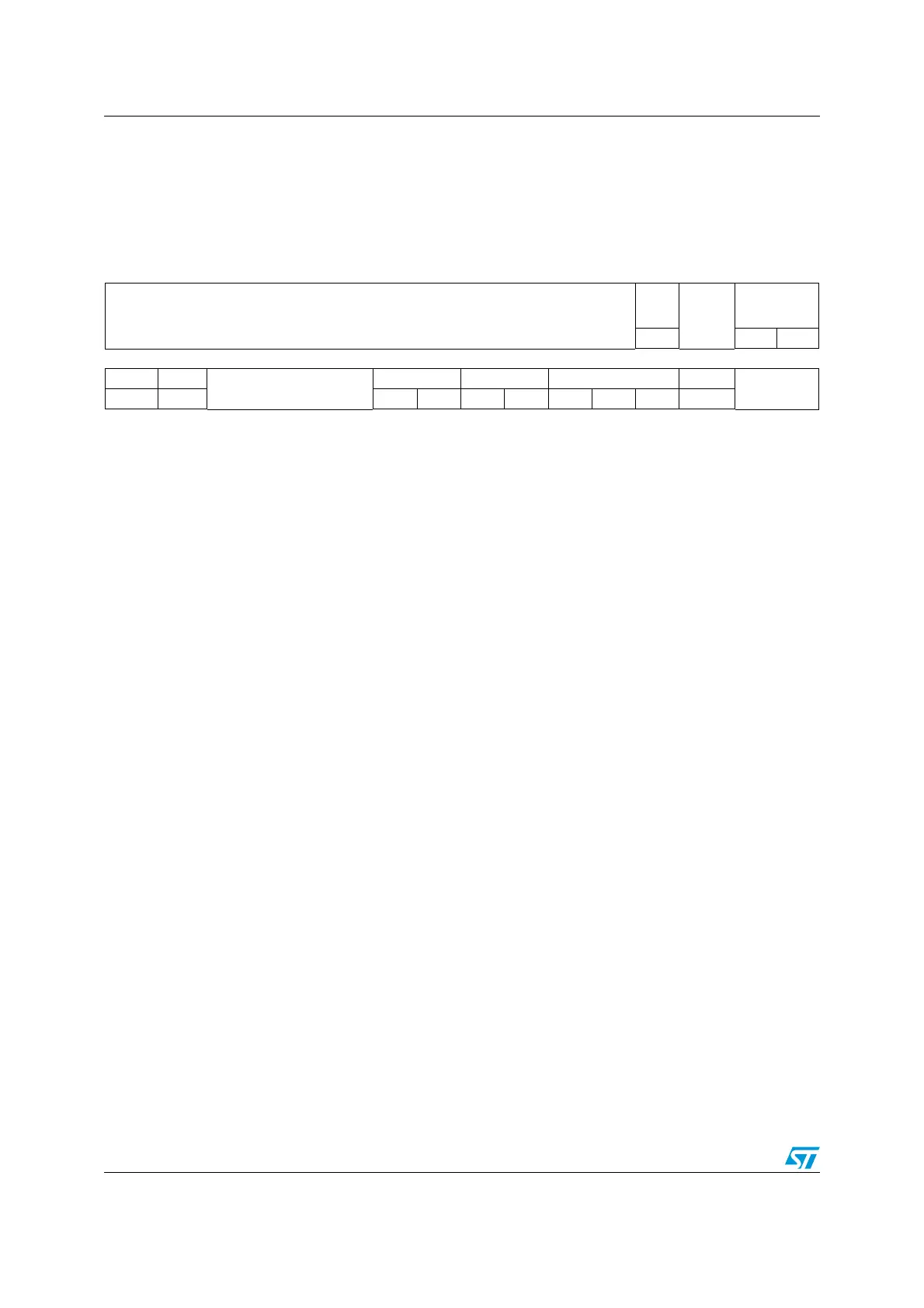

20.6.2 CRYP control register (CRYP_CR) for

STM32F42xxx and STM32F43xxx

Address offset: 0x00

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

ALGO

MODE

[3]

Res.

GCM_CCMPH

rw rw rw

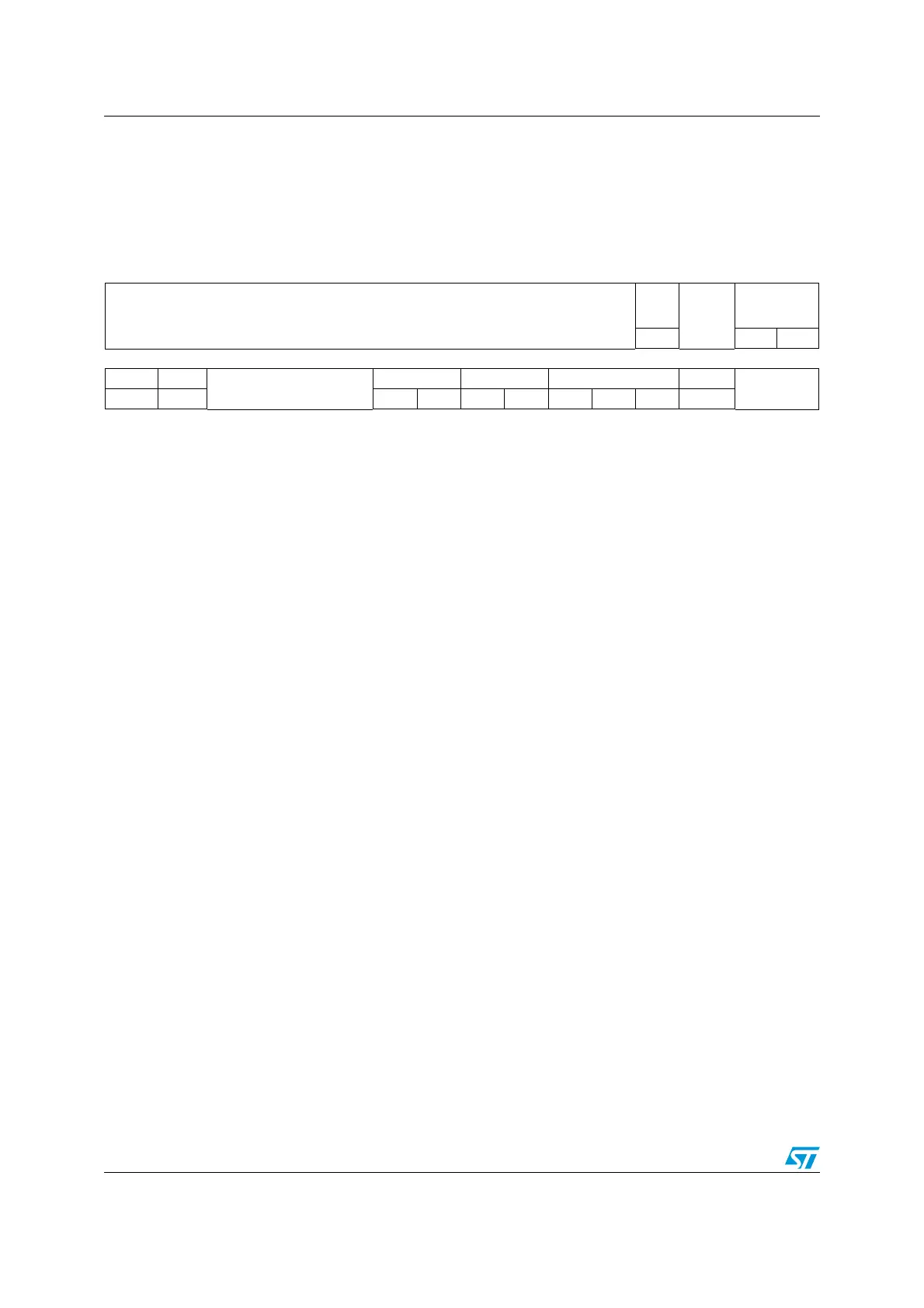

1514131211109876543 2 10

CRYPEN FFLUSH

Reserved

KEYSIZE DATATYPE ALGOMODE[2:0] ALGODIR

Reserved

rw w rwrwrwrwrwrwrw rw

Bit 31:20 Reserved, forced by hardware to 0.

Bit 18 Reserved, forced by hardware to 0.

Bit 17:16 GCM_CCMPH[1:0]: no effect if “GCM or CCM algorithm” is not set

00: GCM_CCM init Phase

01: GCM_CCM header phase

10: GCM_CCM payload phase

11: GCM_CCM final phase

Bit 15 CRYPEN: Cryptographic processor enable

0: CRYP processor is disabled

1: CRYP processor is enabled

Note: The CRYPEN bit is automatically cleared by hardware when the key

preparation process ends (ALGOMODE=111b) or GCM_CCM init Phase

Bit 14 FFLUSH: FIFO flush

When CRYPEN = 0, writing this bit to 1 flushes the IN and OUT FIFOs (that is

read and write pointers of the FIFOs are reset. Writing this bit to 0 has no effect.

When CRYPEN = 1, writing this bit to 0 or 1 has no effect.

Reading this bit always returns 0.

Bits 13:10 Reserved, forced by hardware to 0.

Bits 9:8 KEYSIZE[1:0]: Key size selection (AES mode only)

This bitfield defines the bit-length of the key used for the AES cryptographic core.

This bitfield is ‘don’t care’ in the DES or TDES modes.

00: 128 bit key length

01: 192 bit key length

10: 256 bit key length

11: Reserved, do not use this value

Loading...

Loading...