Ethernet (ETH): media access control (MAC) with DMA controller RM0090

959/1422 Doc ID 018909 Rev 4

frame (for example, because the receive FIFO was full before the time stamp could be

written to it), the DMA writes all ones to RDES2 and RDES3. Otherwise (that is, if time

stamping is not enabled), RDES2 and RDES3 remain unchanged.

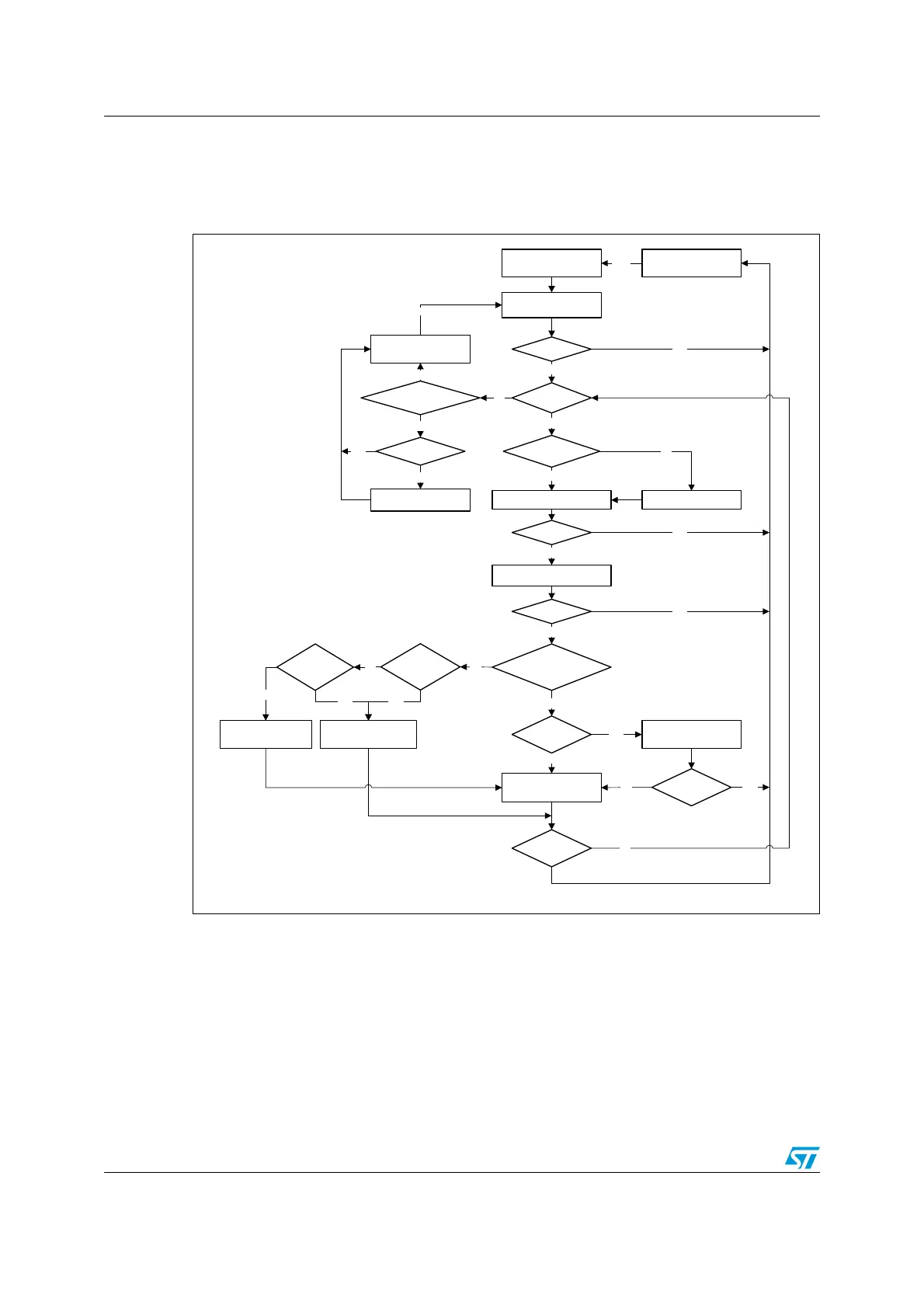

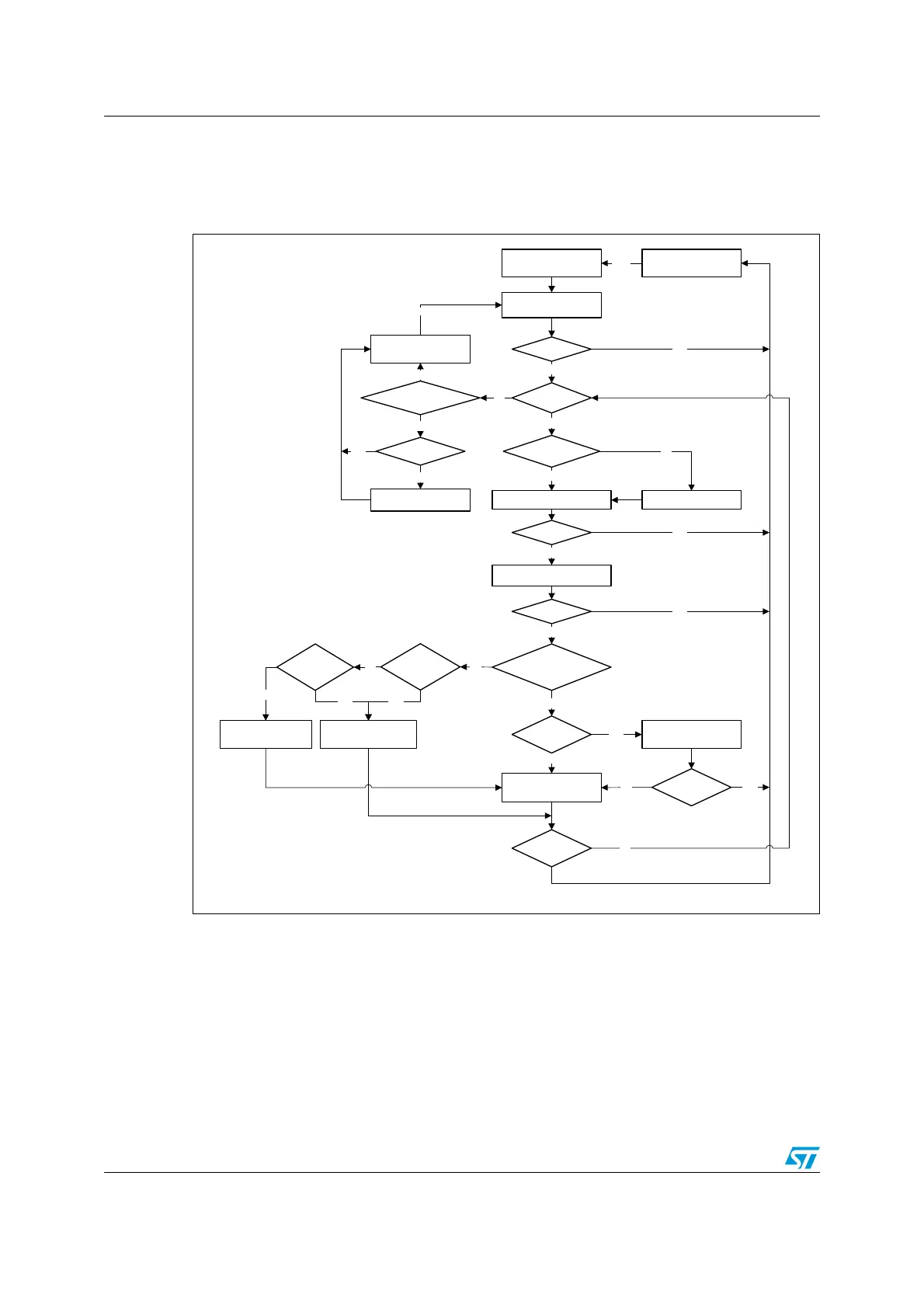

Figure 352. Receive DMA operation

(Re-)Fetch next

descriptor

(AHB)

error?

No

Own bit set?

Yes

Yes

Stop RxDMAStart RxDMA Start

(AHB)

error?

No

RxDMA suspended

Yes

Frame data

available ?

Wait for frame dataWrite data to buffer(s)

Yes

Yes

Fetch next descriptor

Yes

No

Frame transfer

complete?

No

Set descriptor error

Yes

Time stamp

present?

No

Close RDES0 as last

descriptor

Write time stamp to

RDES2 & RDES3

No

(AHB)

error?

Yes

Close RDES0 as

intermediate descriptor

Frame transfer

complete?

No

Flush disabled?

No

Flush the

remaining frame

Yes

Yes

No

No

No

Yes

Yes

Poll demand/

new frame available

No

Yes

(AHB)

error?

(AHB)

error?

No

Own bit set

for next desc?

Flush

disabled ?

ai15643

Loading...

Loading...