Ethernet (ETH): media access control (MAC) with DMA controller RM0090

913/1422 Doc ID 018909 Rev 4

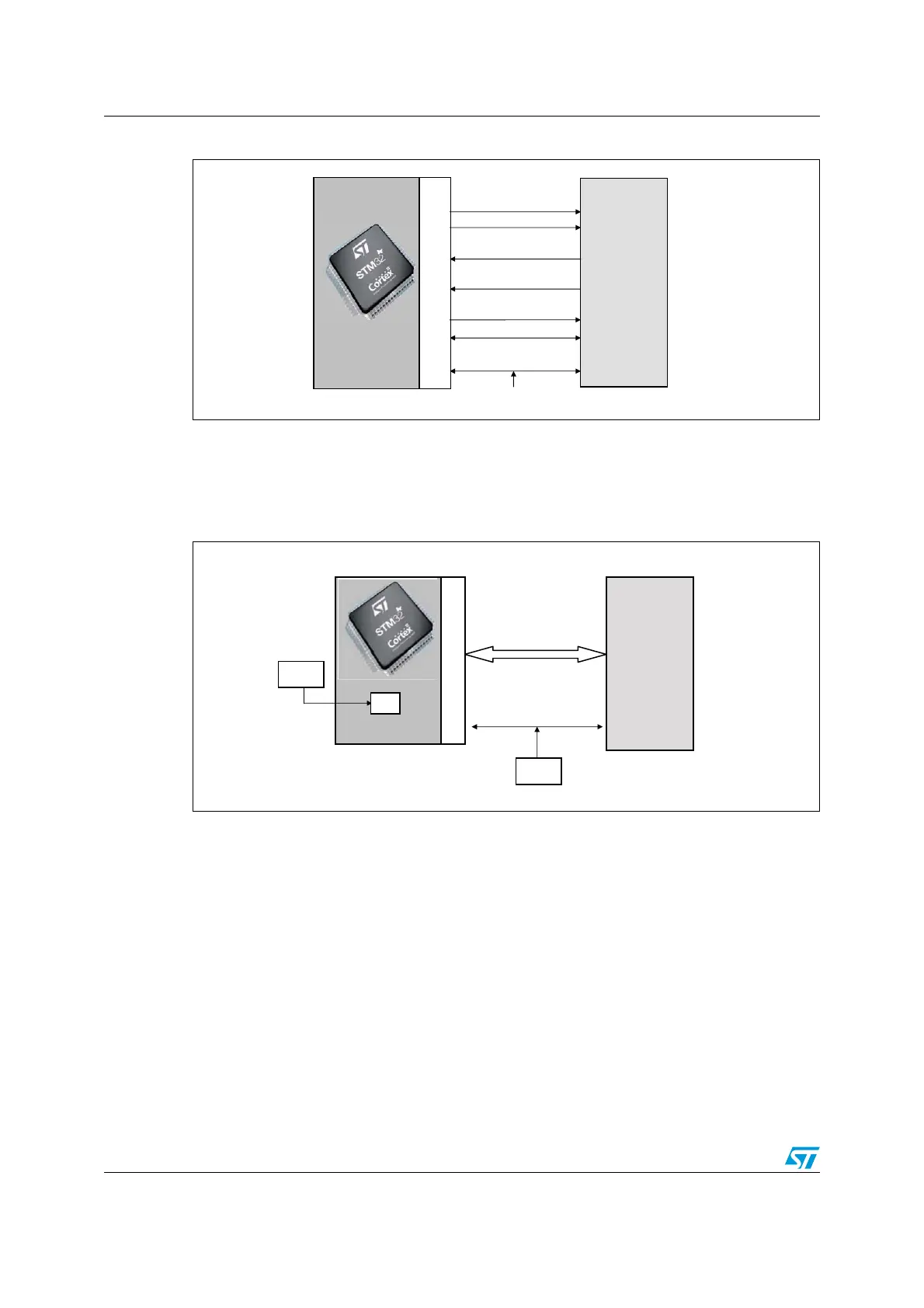

Figure 327. Reduced media-independent interface signals

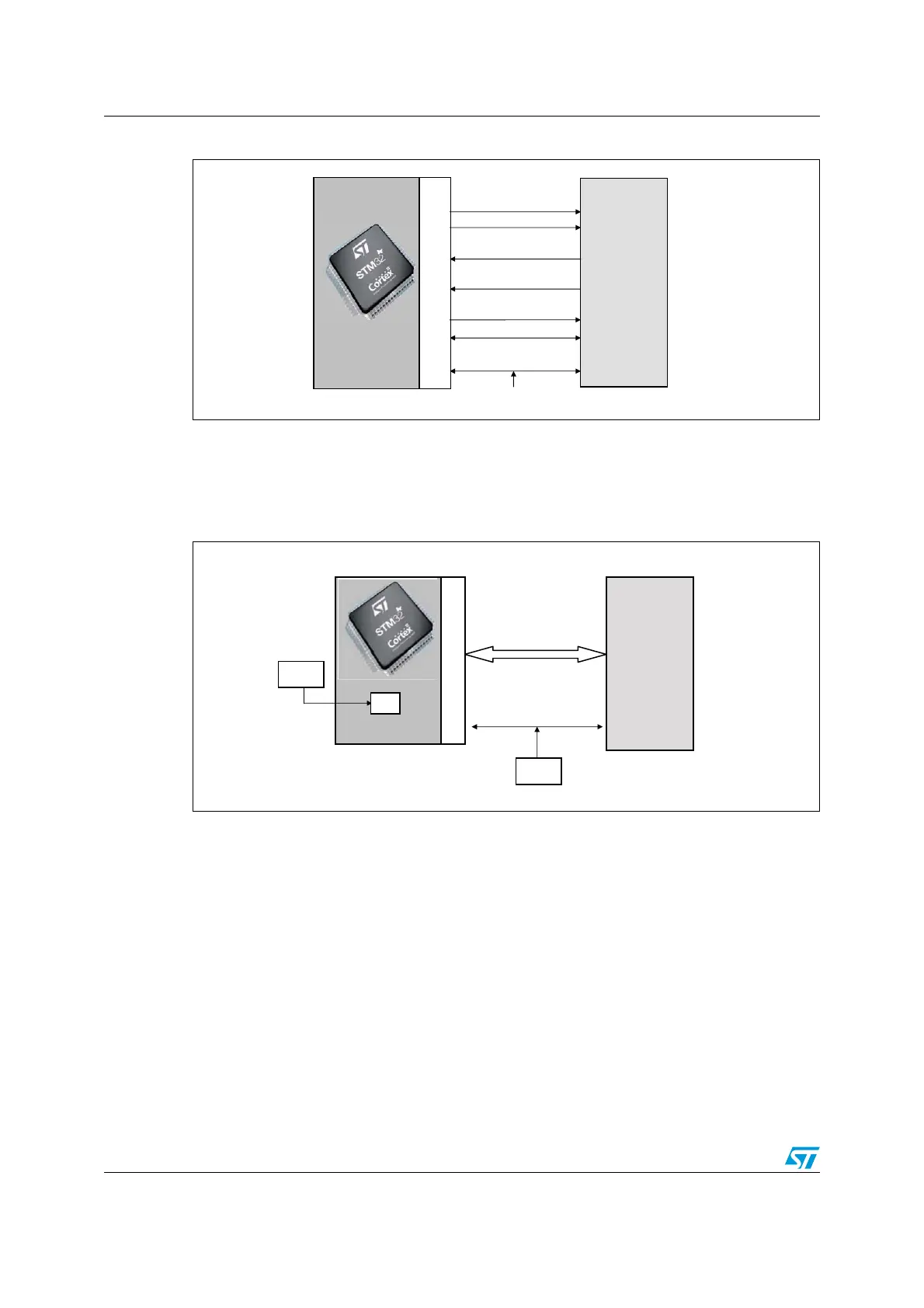

RMII clock sources

Either clock the PHY from an external 50 MHz clock or use a PHY with an embedded PLL to

generate the 50 MHz frequency.

Figure 328. RMII clock sources

29.4.4 MII/RMII selection

The mode, MII or RMII, is selected using the configuration bit 23, MII_RMII_SEL, in the

SYSCFG_PMC register. The application has to set the MII/RMII mode while the Ethernet

controller is under reset or before enabling the clocks.

MII/RMII internal clock scheme

The clock scheme required to support both the MII and RMII, as well as 10 and 100 Mbit/s

operations is described in Figure 329.

STM32

TXD[1:0]

TX_EN

RXD[1:0]

CRS_DV

MDC

MDIO

REF_CLK

Clock source

802.3 MAC

External

PHY

ai15624

MS19930V1

STM32

REF_CLK

50 MHz

25 MHz

PLL

For 10/100 Mbit/s

External

PHY

802.3 MAC

Loading...

Loading...