Flexible static memory controller (FSMC) RM0090

1349/1422 Doc ID 018909 Rev 4

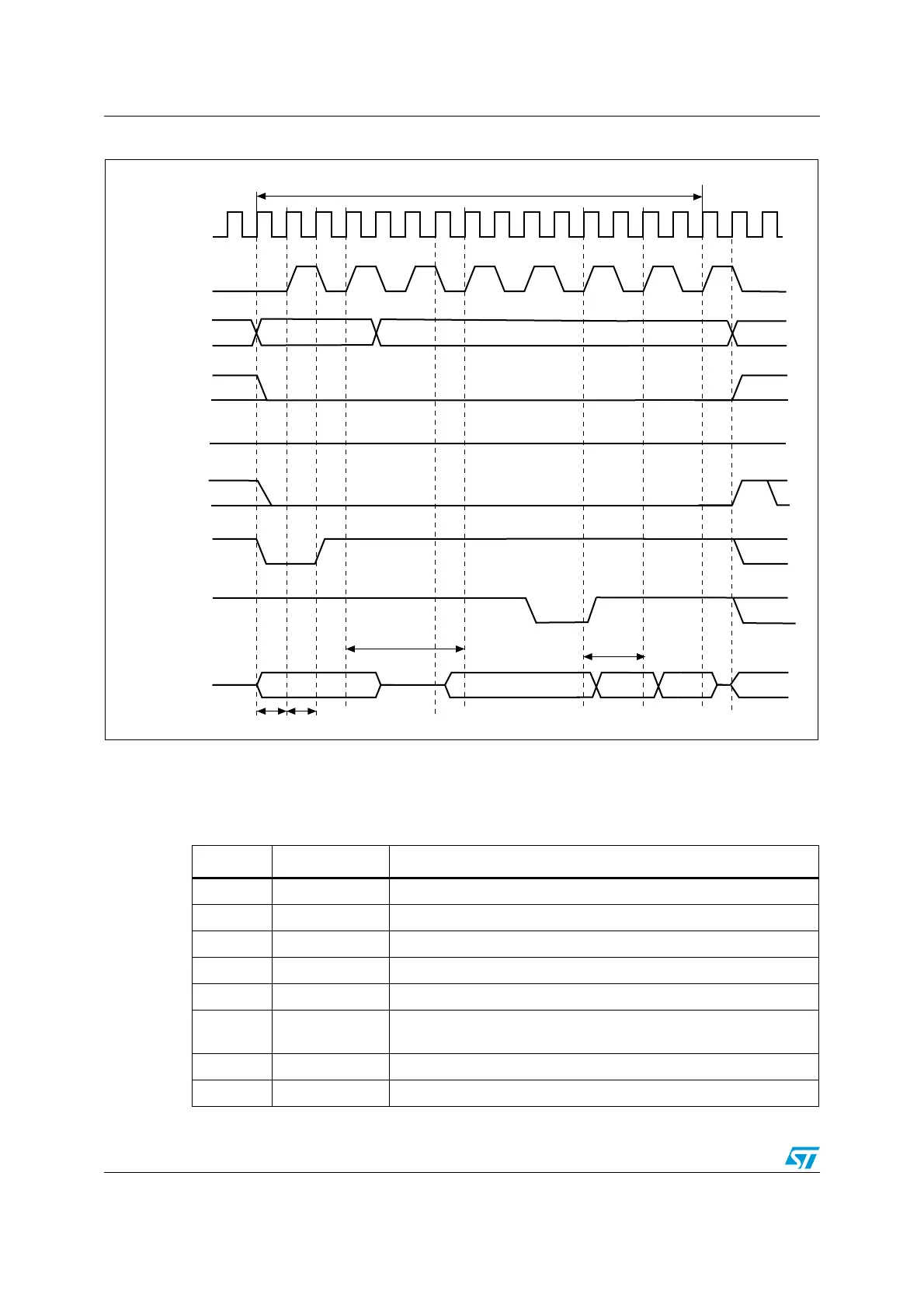

Figure 422. Synchronous multiplexed write mode - PSRAM (CRAM)

1. Memory must issue NWAIT signal one cycle in advance, accordingly WAITCFG must be programmed to 0.

2. NWAIT polarity is set to 0.

3. Byte Lane (NBL) outputs are not shown, they are held low while NEx is active.

Addr[15:0] data

addr[25:16]

Memory transaction = burst of 2 half words

HCLK

CLK

A[25:16]

NEx

NOE

NWE

Hi-Z

NADV

NWAIT

(WAITCFG = 0)

A/D[15:0]

1 clock 1 clock

(DATALAT + 2)

inserted wait state

ai14731e

CLK cycles

data

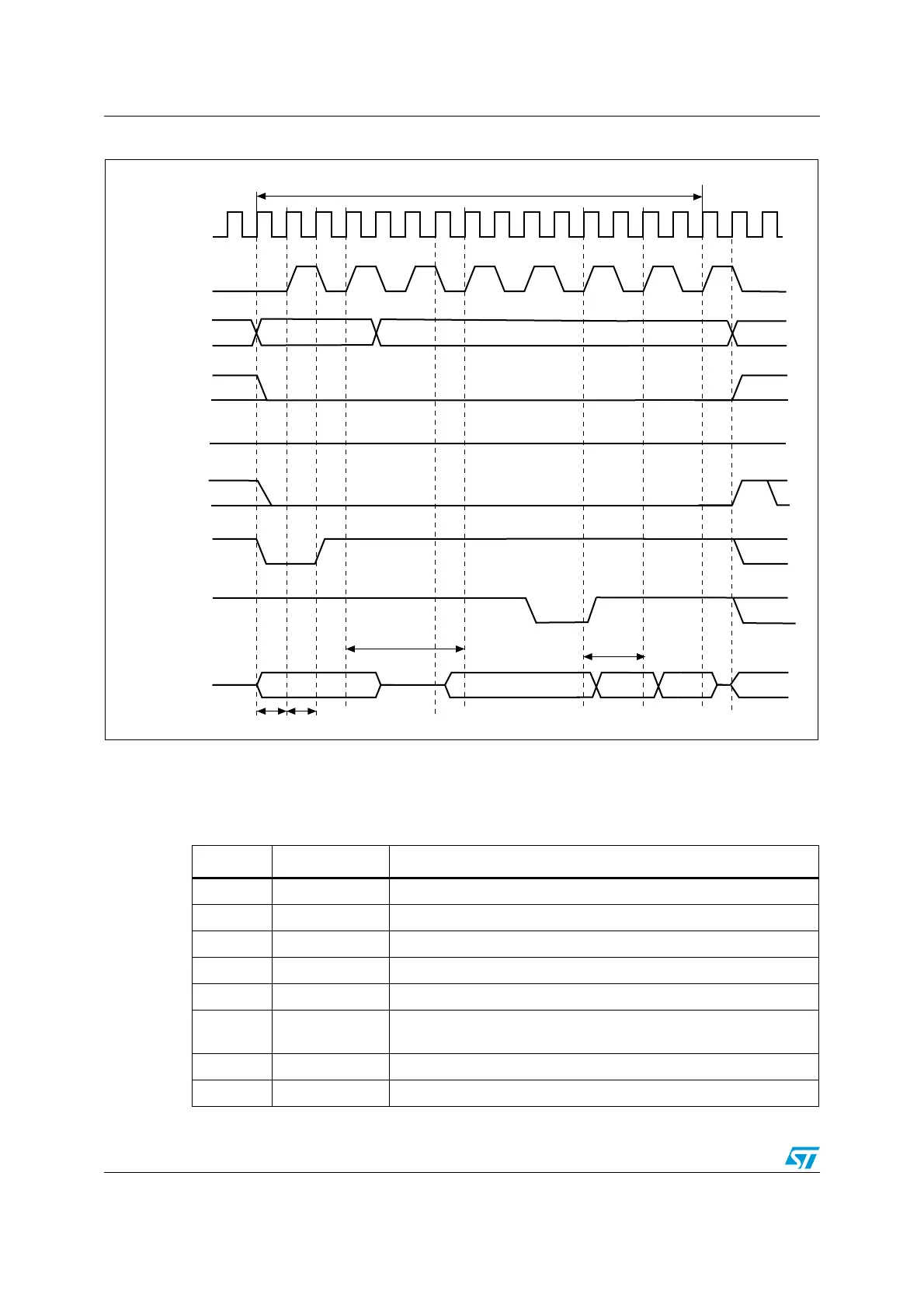

Table 213. FSMC_BCRx bit fields

Bit No. Bit name Value to set

31-20 Reserved 0x000

19 CBURSTRW 0x1

18-16 Reserved 0x0

15 ASCYCWAIT 0x0

14 EXTMOD 0x0

13 WAITEN

to be set to 1 if the memory supports this feature, to be kept at 0

otherwise.

12 WREN no effect on synchronous read

11 WAITCFG 0x0

Loading...

Loading...