Serial peripheral interface (SPI) RM0090

841/1422 Doc ID 018909 Rev 4

27.5.4 SPI data register (SPI_DR)

Address offset: 0x0C

Reset value: 0x0000

27.5.5 SPI CRC polynomial register (SPI_CRCPR) (not used in I

2

S

mode)

Address offset: 0x10

Reset value: 0x0007

Bit 1 TXE: Transmit buffer empty

0: Tx buffer not empty

1: Tx buffer empty

Bit 0 RXNE: Receive buffer not empty

0: Rx buffer empty

1: Rx buffer not empty

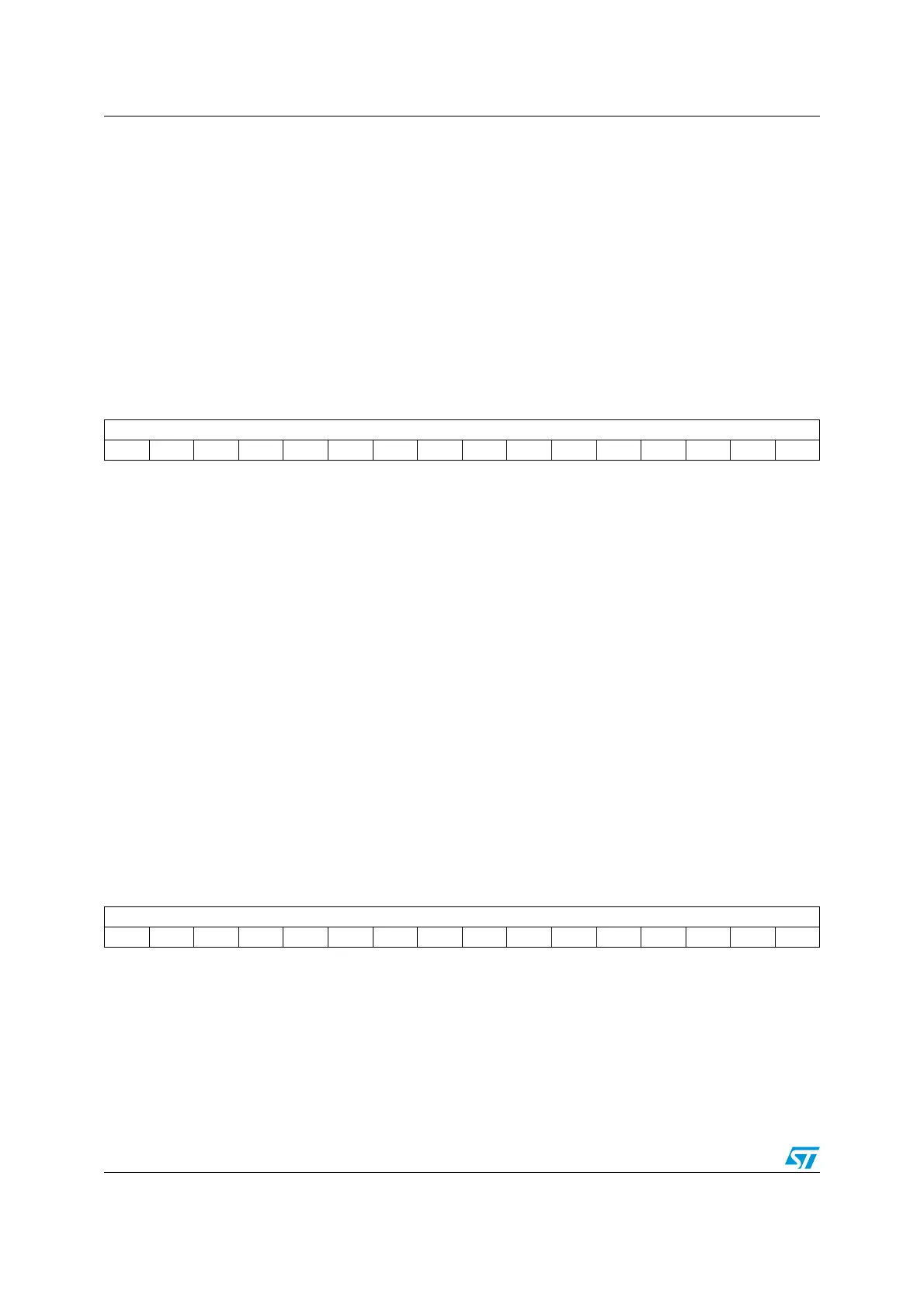

1514131211109876543210

DR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0 DR[15:0]: Data register

Data received or to be transmitted.

The data register is split into 2 buffers - one for writing (Transmit Buffer) and another one for

reading (Receive buffer). A write to the data register will write into the Tx buffer and a read

from the data register will return the value held in the Rx buffer.

Notes for the SPI mode:

Depending on the data frame format selection bit (DFF in SPI_CR1 register), the data

sent or received is either 8-bit or 16-bit. This selection has to be made before enabling

the SPI to ensure correct operation.

For an 8-bit data frame, the buffers are 8-bit and only the LSB of the register

(SPI_DR[7:0]) is used for transmission/reception. When in reception mode, the MSB of

the register (SPI_DR[15:8]) is forced to 0.

For a 16-bit data frame, the buffers are 16-bit and the entire register, SPI_DR[15:0] is

used for transmission/reception.

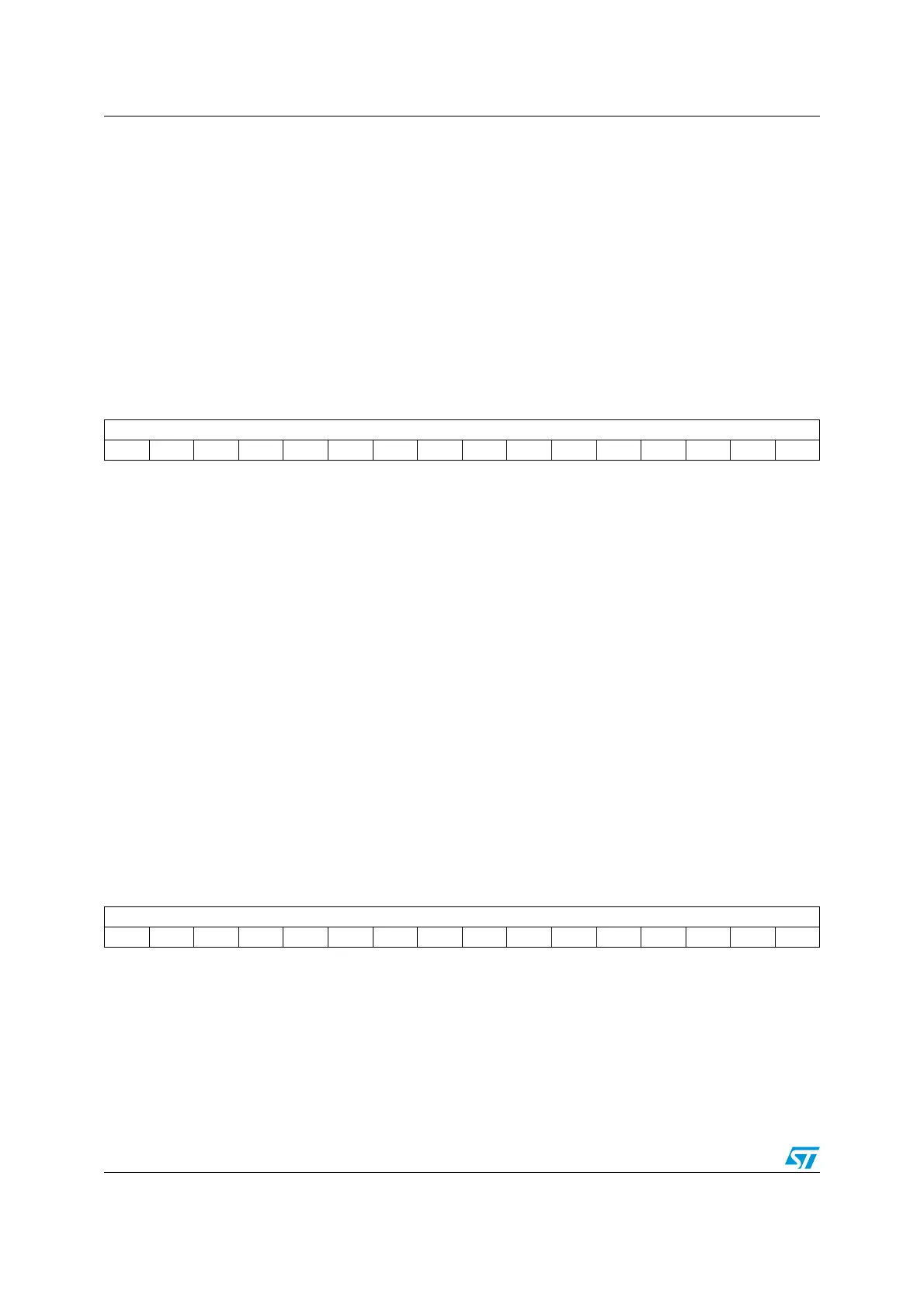

1514131211109876543210

CRCPOLY[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0 CRCPOLY[15:0]: CRC polynomial register

This register contains the polynomial for the CRC calculation.

The CRC polynomial (0007h) is the reset value of this register. Another polynomial can be

configured as required.

Note: Not used for the I

2

S mode.

Loading...

Loading...