DMA controller (DMA) RM0090

235/1422 Doc ID 018909 Rev 4

9.4 DMA interrupts

For each DMA stream, an interrupt can be produced on the following events:

● Half-transfer reached

● Transfer complete

● Transfer error

● Fifo error (overrun, underrun or FIFO level error)

● Direct mode error

Separate interrupt enable control bits are available for flexibility as shown in Ta ble 4 3.

Note: Before setting an Enable control bit to ‘1’, the corresponding event flag should be cleared,

otherwise an interrupt is immediately generated.

9.5 DMA registers

The DMA registers can be accessed by words (32 bits).

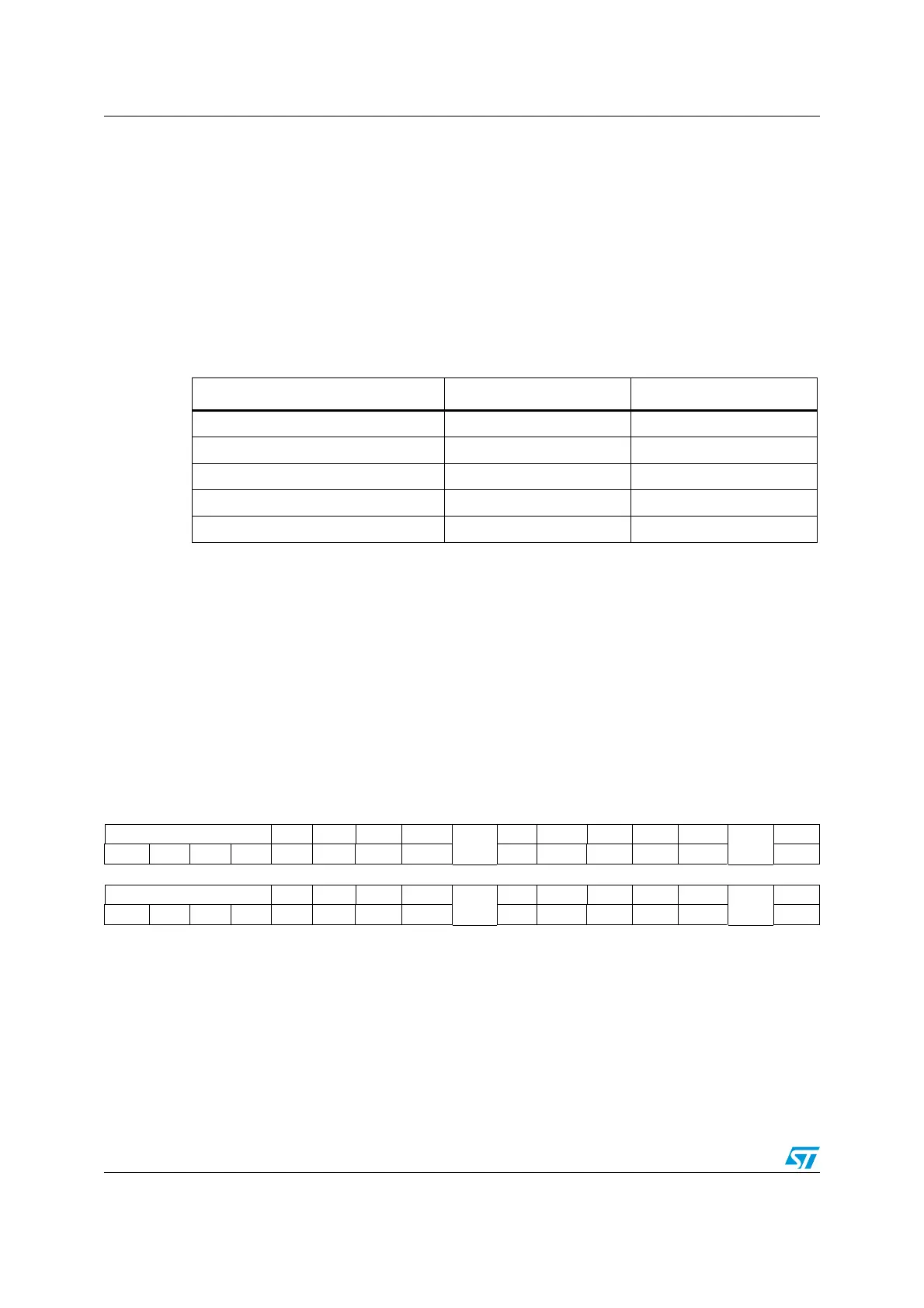

9.5.1 DMA low interrupt status register (DMA_LISR)

Address offset: 0x00

Reset value: 0x0000 0000

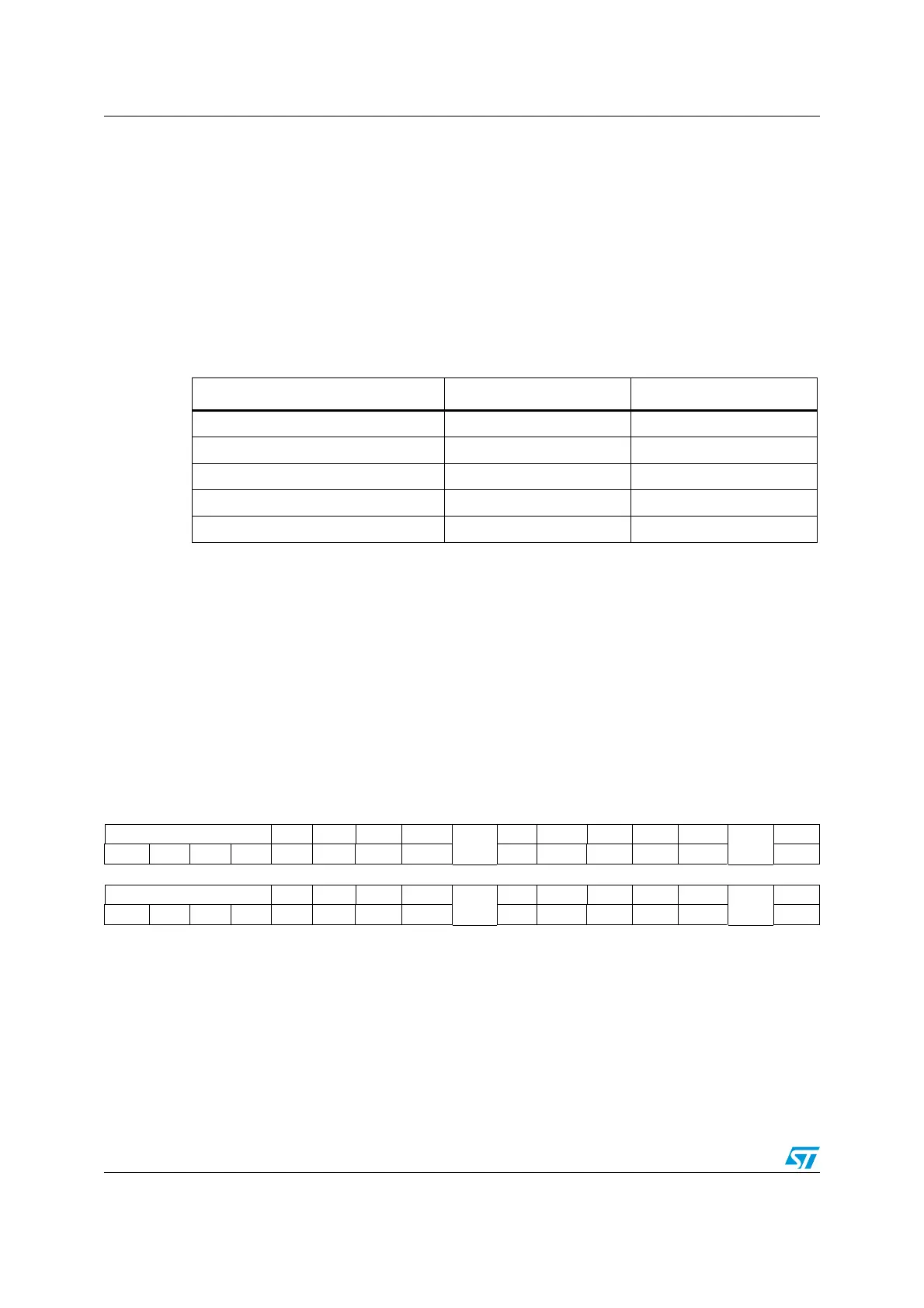

Table 43. DMA interrupt requests

Interrupt event Event flag Enable control bit

Half-transfer HTIF HTIE

Transfer complete TCIF TCIE

Transfer error TEIF TEIE

FIFO overrun/underrun FEIF FEIE

Direct mode error DMEIF DMEIE

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved TCIF3 HTIF3 TEIF3 DMEIF3

Reserv

ed

FEIF3 TCIF2 HTIF2 TEIF2 DMEIF2

Reserv

ed

FEIF2

r rrrr r r r r r r r r r

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved TCIF1 HTIF1 TEIF1 DMEIF1

Reserv

ed

FEIF1 TCIF0 HTIF0 TEIF0 DMEIF0

Reserv

ed

FEIF0

r rrrr r r r r r r r r r

Bits 31:28, 15:12 Reserved, must be kept at reset value.

Bits 27, 21, 11, 5 TCIFx: Stream x transfer complete interrupt flag (x = 3..0)

This bit is set by hardware. It is cleared by software writing 1 to the corresponding bit in the

DMA_LIFCR register.

0: No transfer complete event on stream x

1: A transfer complete event occurred on stream x

Loading...

Loading...