Hash processor (HASH) RM0090

617/1422 Doc ID 018909 Rev 4

22.4.5 HASH digest registers (HASH_HR0..4/5/6/7)

Address offset: 0x0C to 0x1C (STM32F405xx/07xx and STM32F415xx/17xx), plus 0x310 to

0x32C (STM32F42xxx and STM32F43xxx)

Reset value: 0x0000 0000

These registers contain the message digest result named as:

1. H0, H1, H2, H3 and H4, respectively, in the SHA1 algorithm description

Note that in this case, the HASH_H5 to HASH_H7 register is not used, and is read as

zero.

2. A, B, C and D, respectively, in the MD5 algorithm description

Note that in this case, the HASH_H4 to HASH_H7 register is not used, and is read as

zero.

3. H0 to H6, respectively, in the SHA224 algorithm description,

Note that in this case, the HASH_H7 register is not used, and is read as zero.

4. H0 to H7, respectively, in the SHA256 algorithm description,

If a read access to one of these registers occurs while the HASH core is calculating an

intermediate digest or a final message digest (that is when the DCAL bit has been written to

1), then the read is stalled until the completion of the HASH calculation.

Note: H0, H1, H2, H3 and H4 mapping are duplicated in two region.

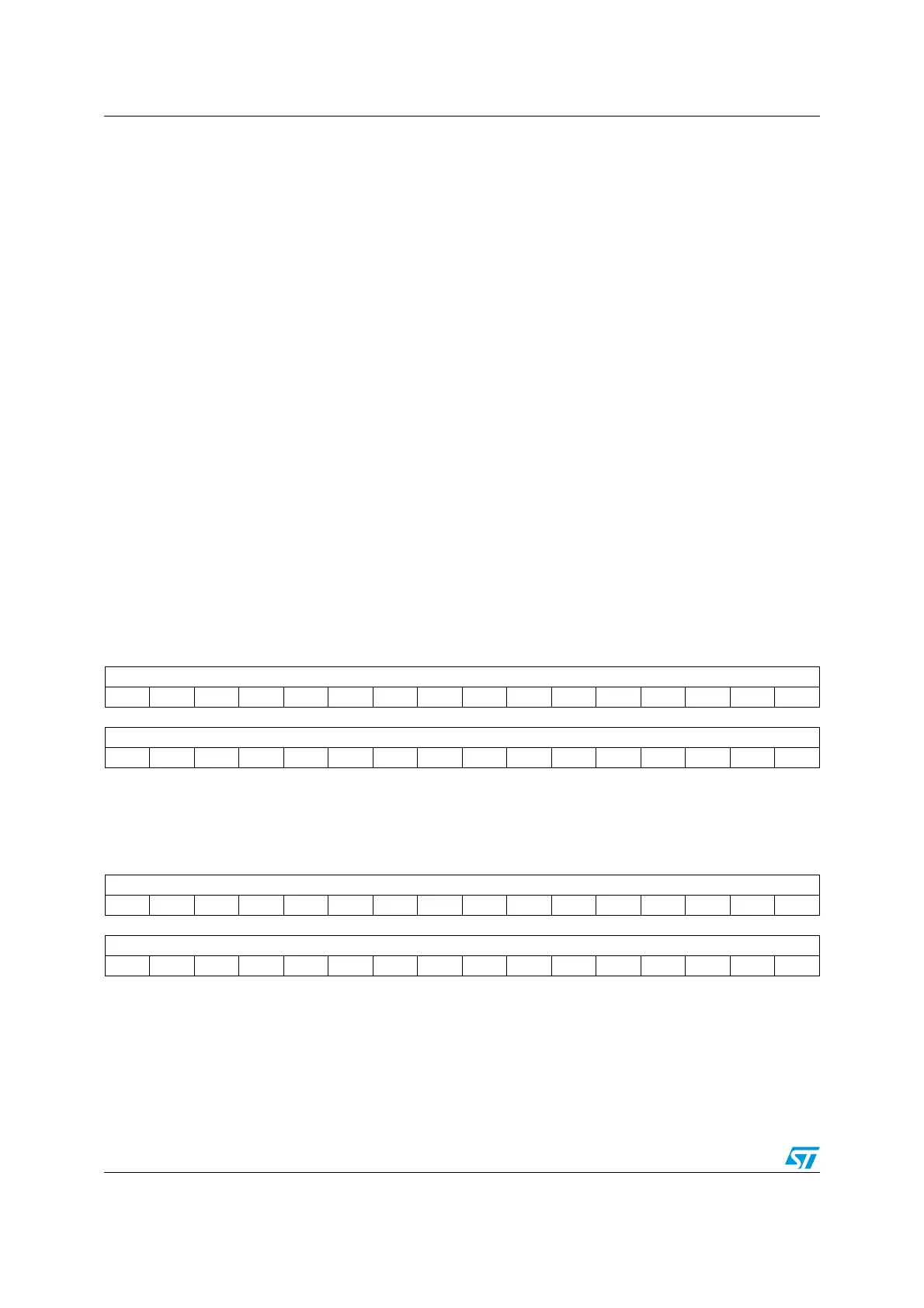

HASH_HR0

Address offset: 0x0C and 0x310

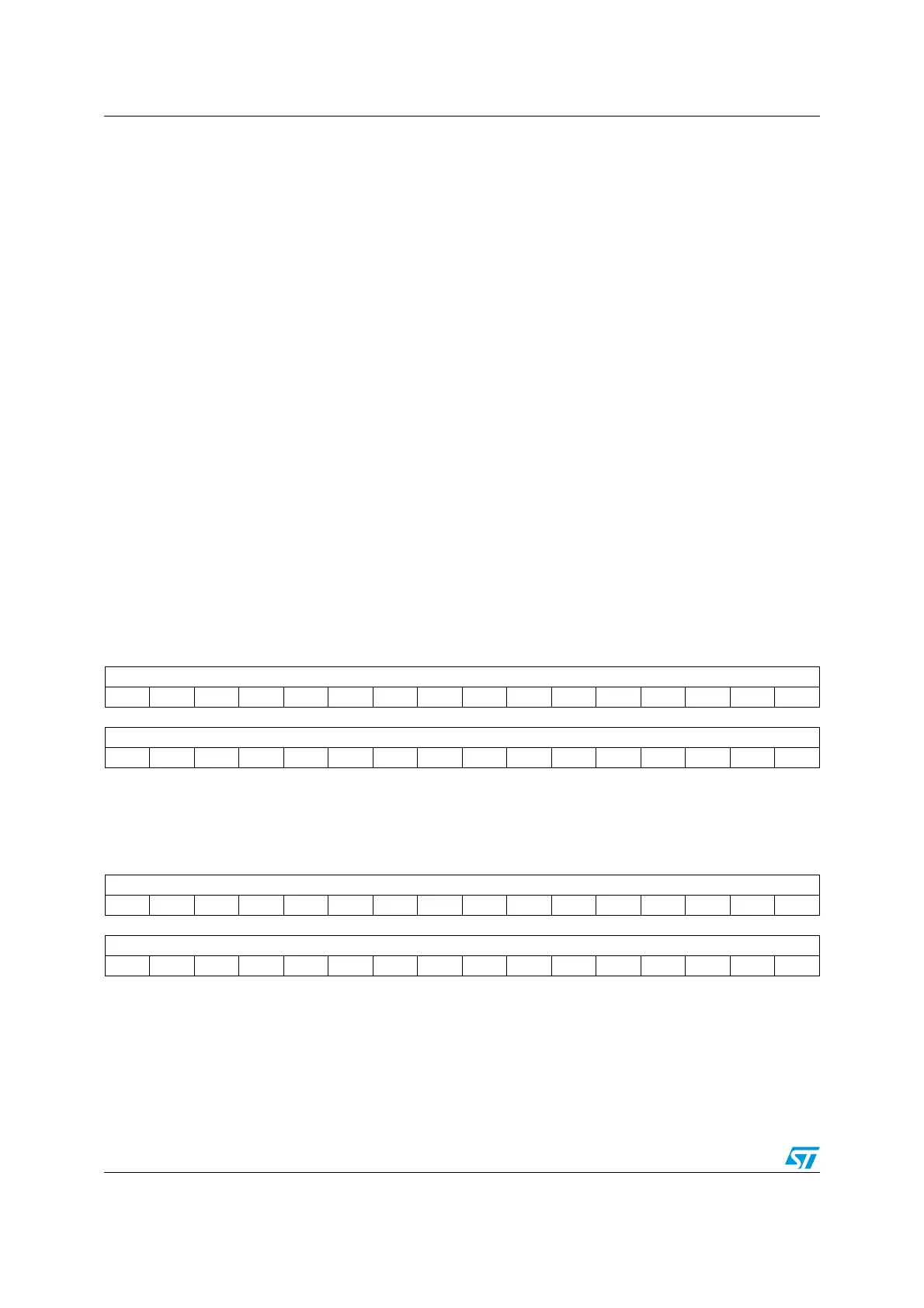

HASH_HR1

Address offset: 0x10 and 0x314

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

H0

rrrrrrrrrrrrrrrr

1514131211109876543210

H0

rrrrrrrrrrrrrrrr

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

H1

rrrrrrrrrrrrrrrr

1514131211109876543210

H1

rrrrrrrrrrrrrrrr

Loading...

Loading...