RM0090 USB on-the-go high-speed (OTG_HS)

Doc ID 018909 Rev 4 1310/1422

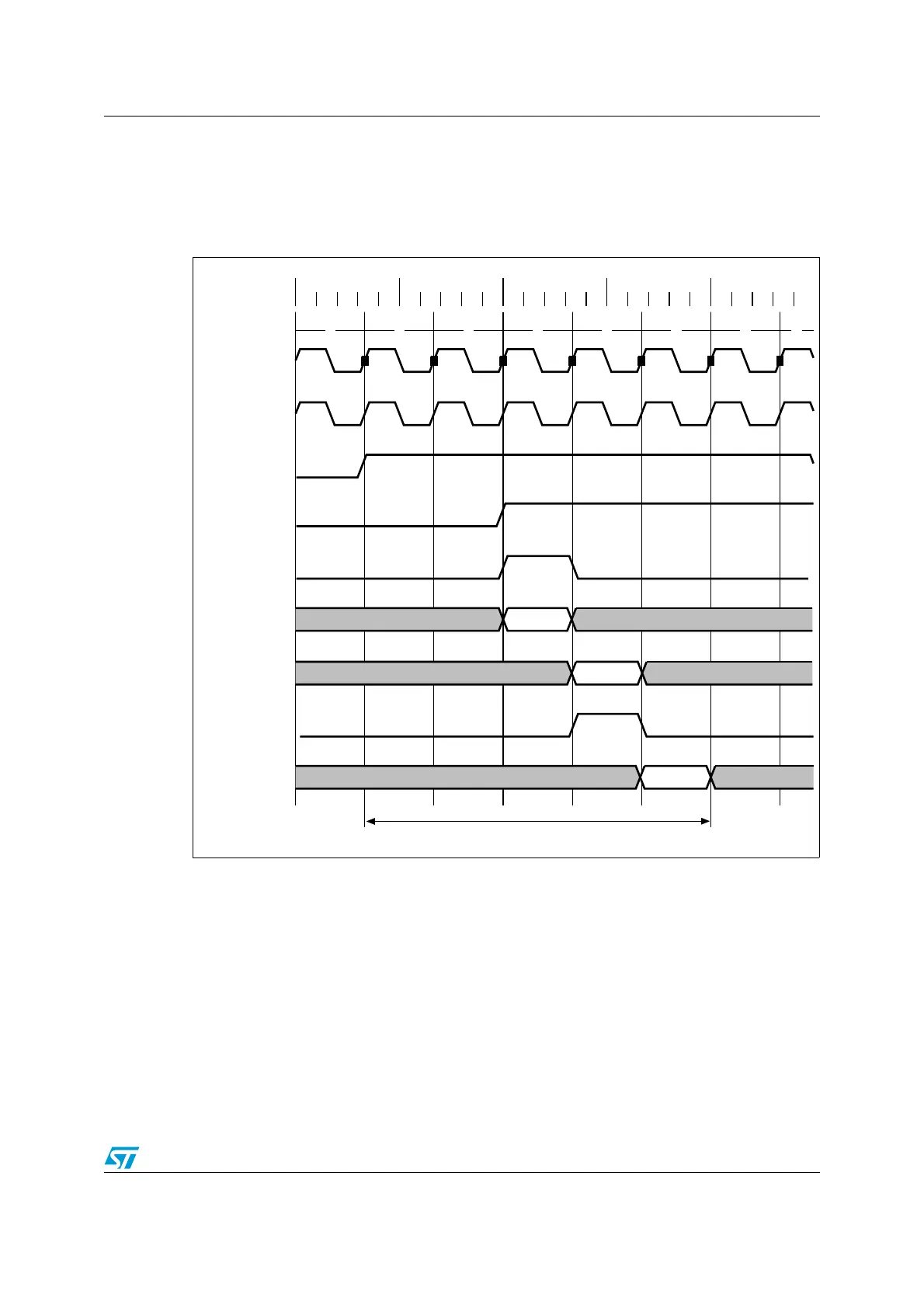

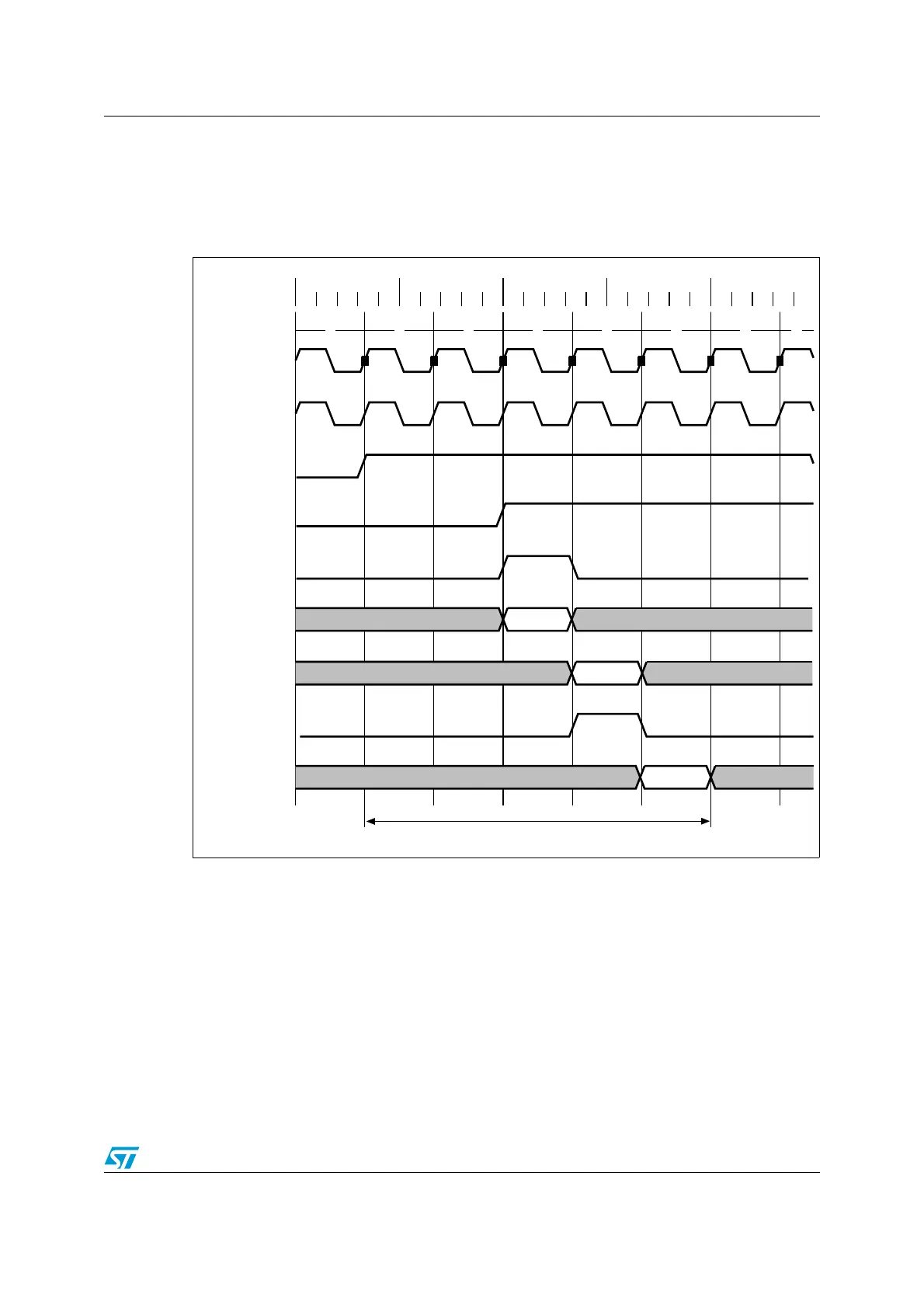

The application can use the following formula to calculate the value of TRDT:

4 × AHB clock + 1 PHY clock = (2 clock sync + 1 clock memory address + 1 clock

memory data from sync RAM) + (1 PHY clock (next PHY clock MAC can sample the 2

clock FIFO outputs)

Figure 398. TRDT max timing case

31.13.9 OTG programming model

The OTG_HS controller is an OTG device supporting HNP and SRP. When the core is

connected to an “A” plug, it is referred to as an A-device. When the core is connected to a

“B” plug it is referred to as a B-device. In host mode, the OTG_HS controller turns off V

BUS

to conserve power. SRP is a method by which the B-device signals the A-device to turn on

V

BUS

power. A device must perform both data-line pulsing and V

BUS

pulsing, but a host can

detect either data-line pulsing or V

BUS

pulsing for SRP. HNP is a method by which the B-

device negotiates and switches to host role. In Negotiated mode after HNP, the B-device

suspends the bus and reverts to the device role.

12345678

0ns 50ns 100ns 150ns 200ns

HCLK

PCLK

tkn_rcvd

dsynced_tkn_rcvd

spr_read

spr_addr

spr_rdata

srcbuf_push

srcbuf_rdata

5 Clocks

D1

A1

D1

ai15680

Loading...

Loading...