Digital-to-analog converter (DAC) RM0090

329/1422 Doc ID 018909 Rev 4

12.5.15 DAC register map

Tabl e 5 9 summarizes the DAC registers.

Refer to Table 2 on page 52 for the register boundary addresses.

Bits 31:30 Reserved, must be kept at reset value.

Bit 29 DMAUDR2: DAC channel2 DMA underrun flag

This bit is set by hardware and cleared by software (by writing it to 1).

0: No DMA underrun error condition occurred for DAC channel2

1: DMA underrun error condition occurred for DAC channel2 (the currently selected trigger is

driving DAC channel2 conversion at a frequency higher than the DMA service capability rate)

Bits 28:14 Reserved, must be kept at reset value.

Bit 13 DMAUDR1: DAC channel1 DMA underrun flag

This bit is set by hardware and cleared by software (by writing it to 1).

0: No DMA underrun error condition occurred for DAC channel1

1: DMA underrun error condition occurred for DAC channel1 (the currently selected trigger is

driving DAC channel1 conversion at a frequency higher than the DMA service capability rate)

Bits 12:0 Reserved, must be kept at reset value.

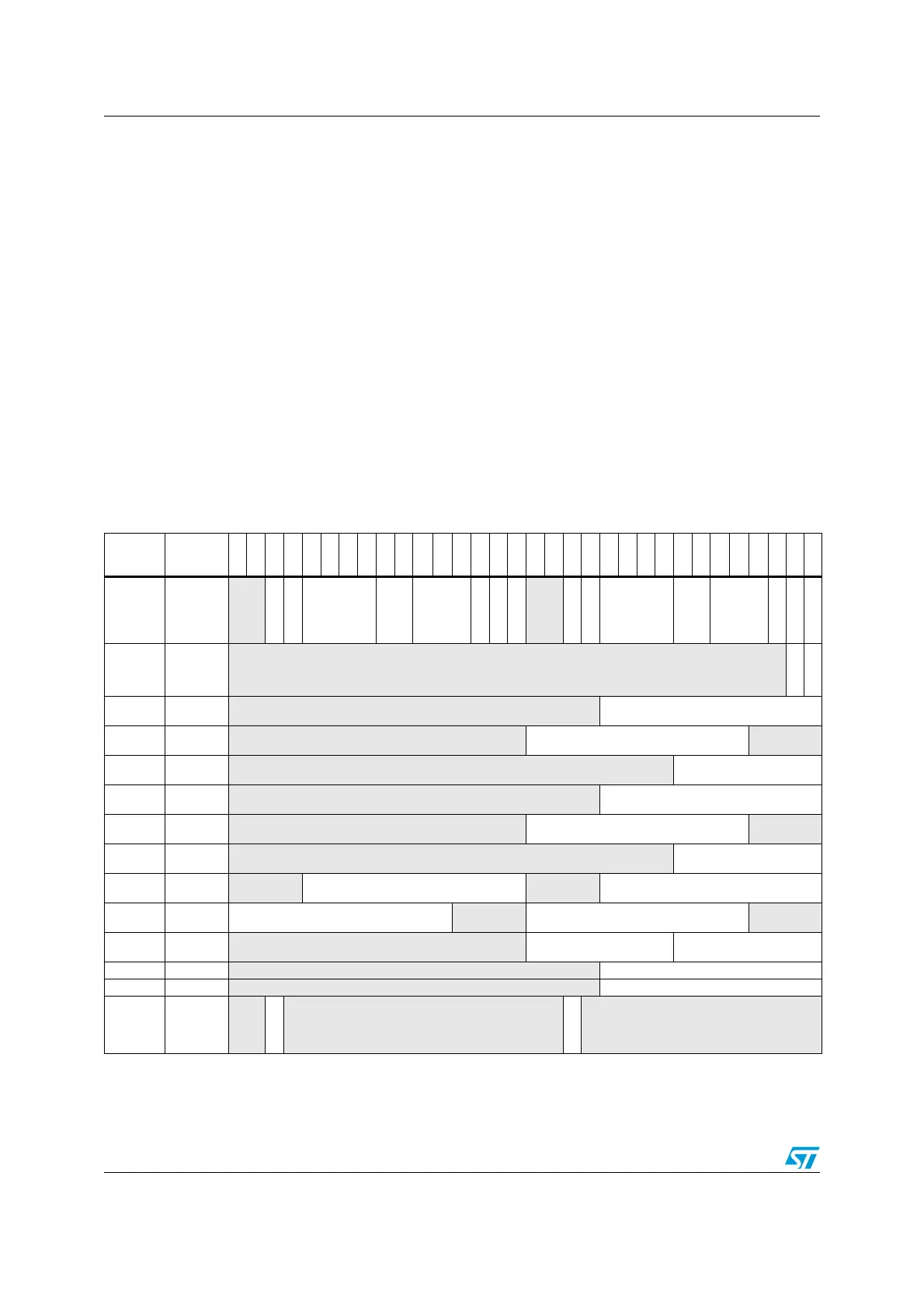

Table 59. DAC register map

Address

offset

Register

name

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00 DAC_CR

Reserved

DMAUDRIE2

DMAEN2

MAMP2[3:0]

WAVE

2[2:0]

TSEL2[2:0]

TEN2

BOFF2

EN2

Reserved

DMAUDRIE1

DMAEN1

MAMP1[3:0]

WAVE

1[2:0]

TSEL1[2:0]

TEN1

BOFF1

EN1

0x04

DAC_SWT

RIGR

Reserved

SWTRIG2

SWTRIG1

0x08

DAC_DHR1

2R1

Reserved DACC1DHR[11:0]

0x0C

DAC_DHR1

2L1

Reserved DACC1DHR[11:0] Reserved

0x10

DAC_DHR8

R1

Reserved DACC1DHR[7:0]

0x14

DAC_DHR1

2R2

Reserved DACC2DHR[11:0]

0x18

DAC_DHR1

2L2

Reserved DACC2DHR[11:0] Reserved

0x1C

DAC_DHR8

R2

Reserved DACC2DHR[7:0]

0x20

DAC_DHR1

2RD

Reserved DACC2DHR[11:0] Reserved DACC1DHR[11:0]

0x24

DAC_DHR1

2LD

DACC2DHR[11:0]

Reserved DACC1DHR[11:0] Reserved

0x28

DAC_DHR8

RD

Reserved DACC2DHR[7:0] DACC1DHR[7:0]

0x2C DAC_DOR1

Reserved DACC1DOR[11:0]

0x30 DAC_DOR2

Reserved DACC2DOR[11:0]

0x34 DAC_SR

Reserved

DMAUDR2

Reserved

DMAUDR1

Reserved

Loading...

Loading...