USB on-the-go high-speed (OTG_HS) RM0090

1295/1422 Doc ID 018909 Rev 4

1. Program the OTG_HS_DOEPTSIZx register.

– STUPCNT = 3

2. Wait for the RXFLVL interrupt (OTG_HS_GINTSTS) and empty the data packets from

the receive FIFO.

3. Assertion of the STUP interrupt (OTG_HS_DOEPINTx) marks a successful completion

of the SETUP Data Transfer.

– On this interrupt, the application must read the OTG_HS_DOEPTSIZx register to

determine the number of SETUP packets received and process the last received

SETUP packet.

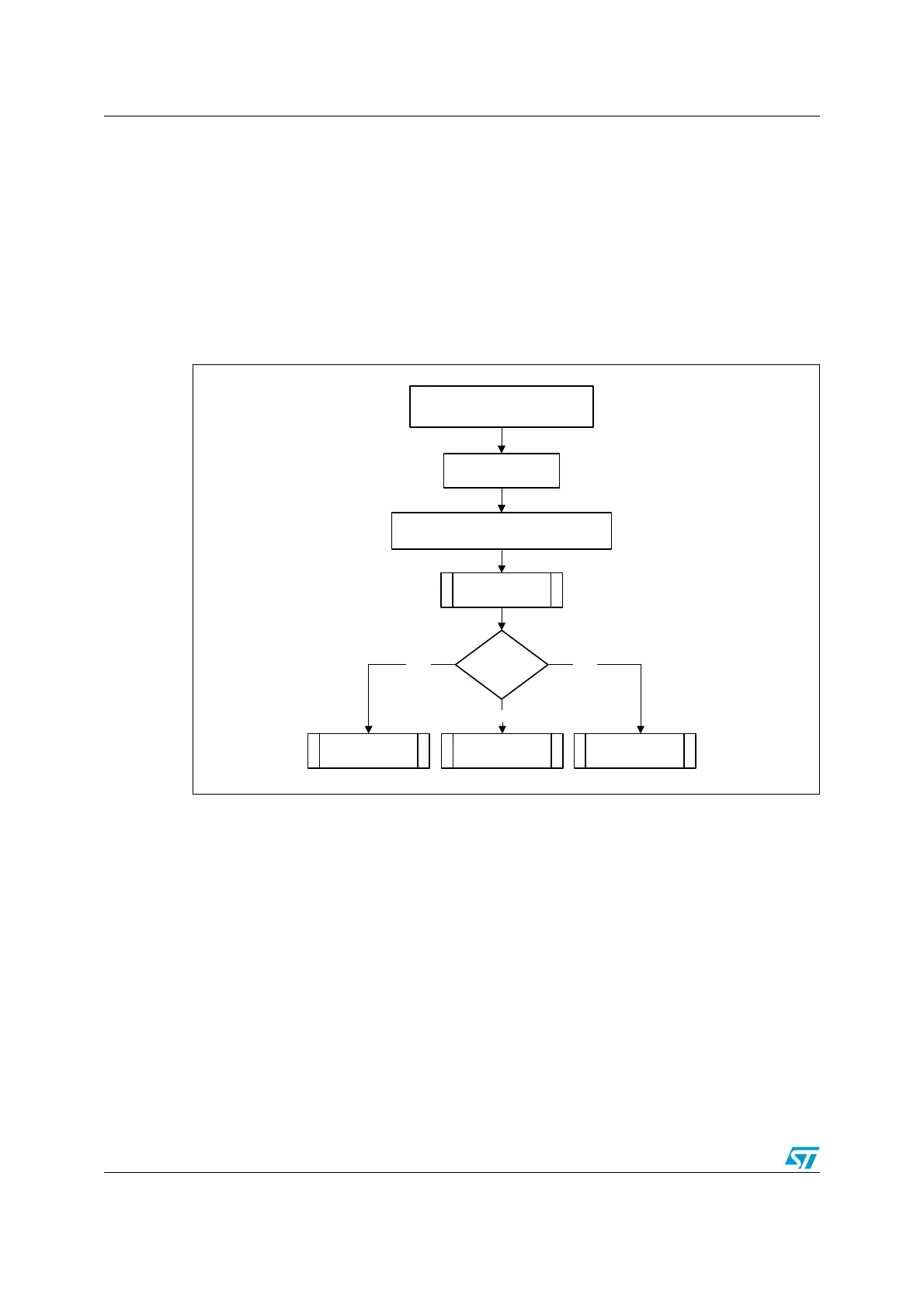

Figure 396. Processing a SETUP packet

● Handling more than three back-to-back SETUP packets

Per the USB 2.0 specification, normally, during a SETUP packet error, a host does not send

more than three back-to-back SETUP packets to the same endpoint. However, the USB 2.0

specification does not limit the number of back-to-back SETUP packets a host can send to

the same endpoint. When this condition occurs, the OTG_HS controller generates an

interrupt (B2BSTUP in OTG_HS_DOEPINTx).

● Setting the global OUT NAK

Internal data flow:

1. When the application sets the Global OUT NAK (SGONAK bit in OTG_HS_DCTL), the

core stops writing data, except SETUP packets, to the receive FIFO. Irrespective of the

space availability in the receive FIFO, nonisochronous OUT tokens receive a NAK

handshake response, and the core ignores isochronous OUT data packets

2. The core writes the Global OUT NAK pattern to the receive FIFO. The application must

reserve enough receive FIFO space to write this data pattern.

Wait for STUP in OTG_FS_DOEPINTx

rem_supcnt =

rd_reg(DOEPTSIZx)

setup_cmd[31:0] = mem[4 – 2 * rem_supcnt]

setup_cmd[63:32] = mem[5 – 2 * rem_supcnt]

ctrl-rd/wr/2 stage

Find setup cmd type

Write

2-stage

Read

setup_np_in_pkt

Status IN phase

rcv_out_pkt

Data OUT phase

setup_np_in_pkt

Data IN phase

ai15678

Loading...

Loading...