Flexible static memory controller (FSMC) RM0090

1337/1422 Doc ID 018909 Rev 4

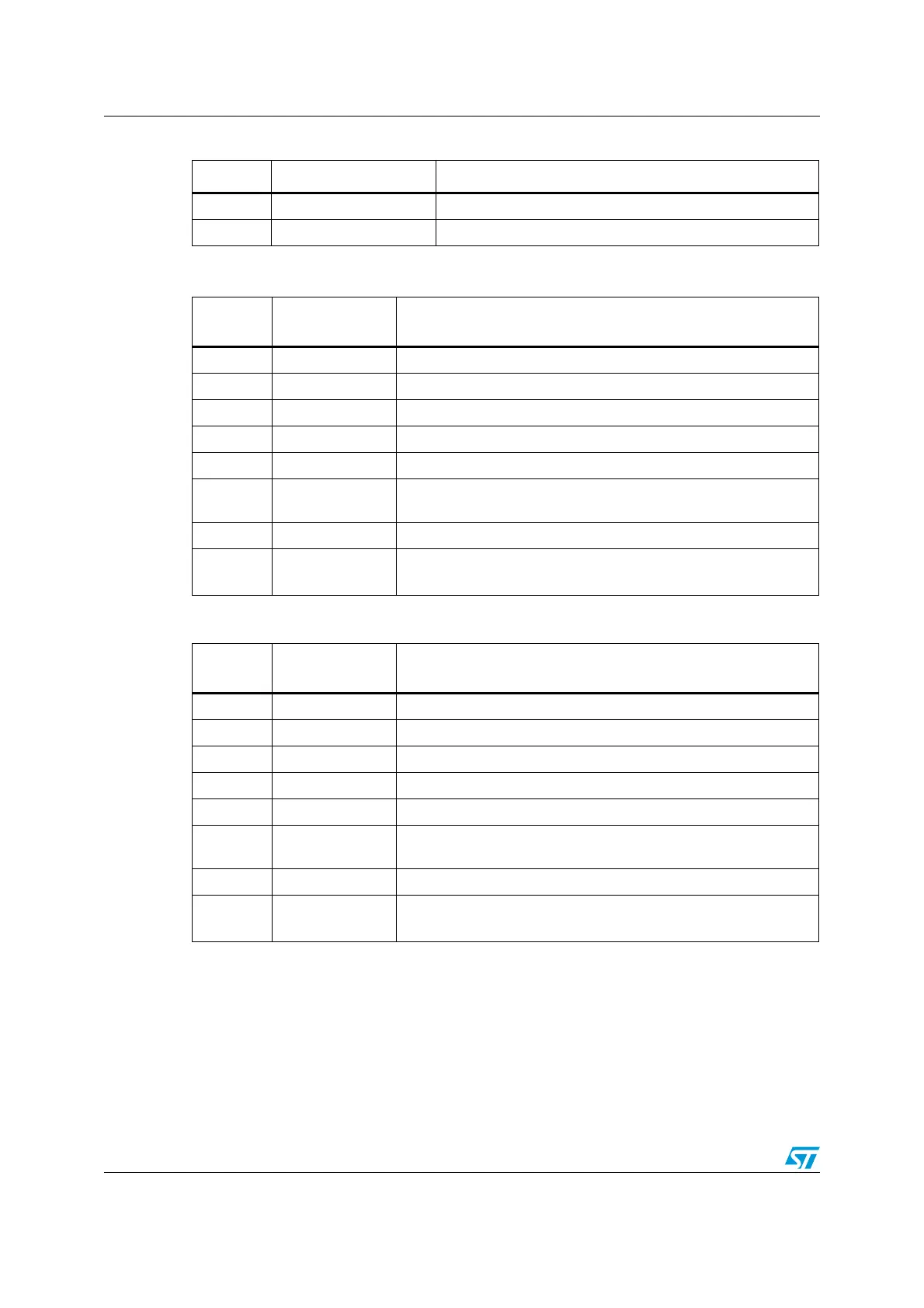

1 MUXEN 0x0

0 MBKEN 0x1

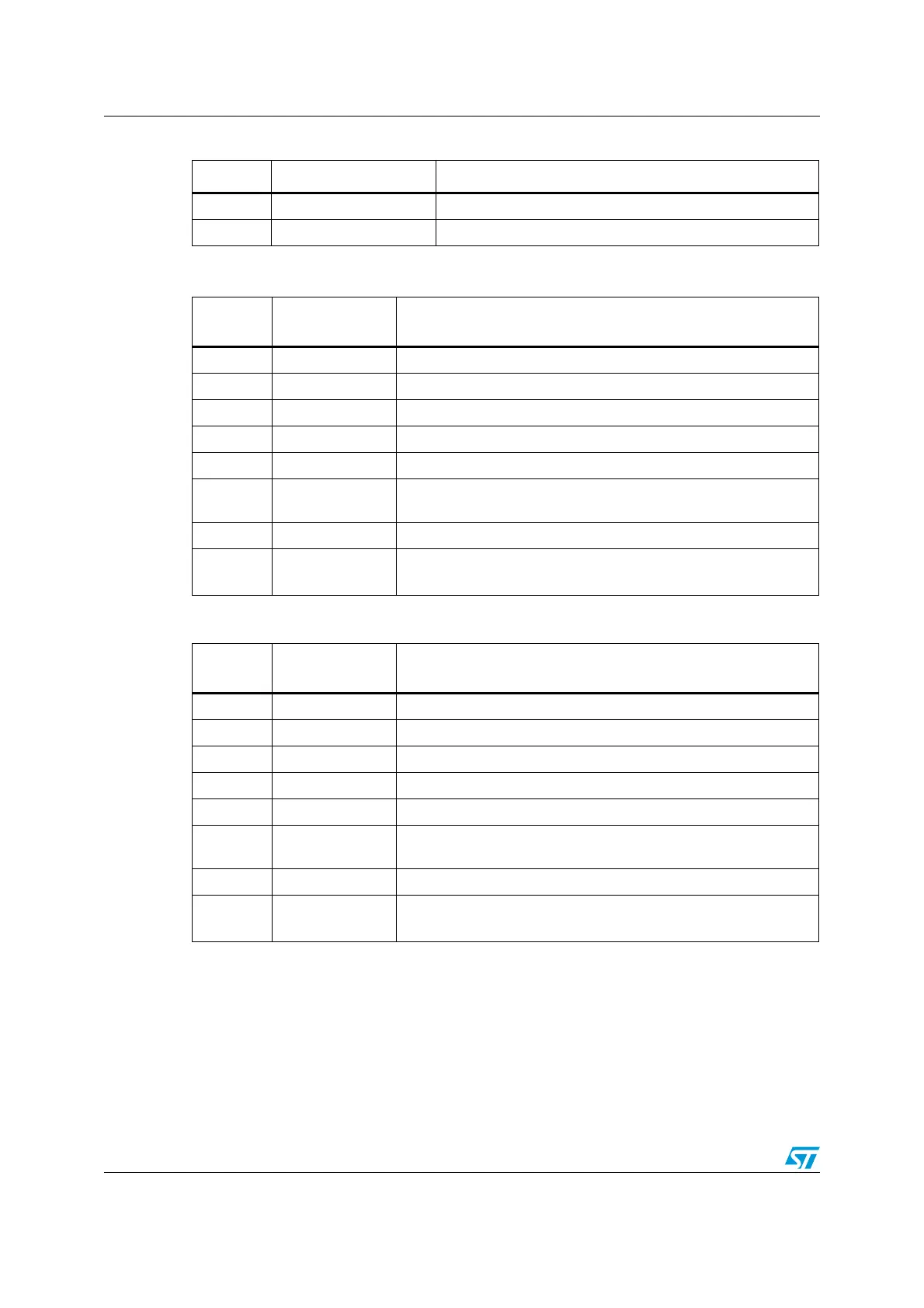

Table 204. FSMC_BTRx bit fields

Bit

number

Bit name Value to set

31:30 Reserved 0x0

29-28 ACCMOD 0x2

27-24 DATLAT 0x0

23-20 CLKDIV 0x0

19-16 BUSTURN Time between NEx high to NEx low (BUSTURN HCLK)

15-8 DATAST

Duration of the second access phase (DATAST+1 HCLK cycles for

write accesses, DATAST HCLK cycles for read accesses).

7-4 ADDHLD Don’t care

3-0 ADDSET

Duration of the first access phase (ADDSET HCLK cycles).

Minimum value for ADDSET is 0.

Table 205. FSMC_BWTRx bit fields

Bit

number

Bit name Value to set

31:30 Reserved 0x0

29-28 ACCMOD 0x2

27-24 DATLAT Don’t care

23-20 CLKDIV Don’t care

19-16 BUSTURN Time between NEx high to NEx low (BUSTURN HCLK)

15-8 DATAST

Duration of the second access phase (DATAST+1 HCLK cycles for

write accesses,

7-4 ADDHLD Don’t care

3-0 ADDSET

Duration of the first access phase (ADDSET HCLK cycles).

Minimum value for ADDSET is 0.

Table 203. FSMC_BCRx bit fields (continued)

Bit No. Bit name Value to set

Loading...

Loading...