Revision history RM0090

1413/1422 Doc ID 018909 Rev 4

Revision history

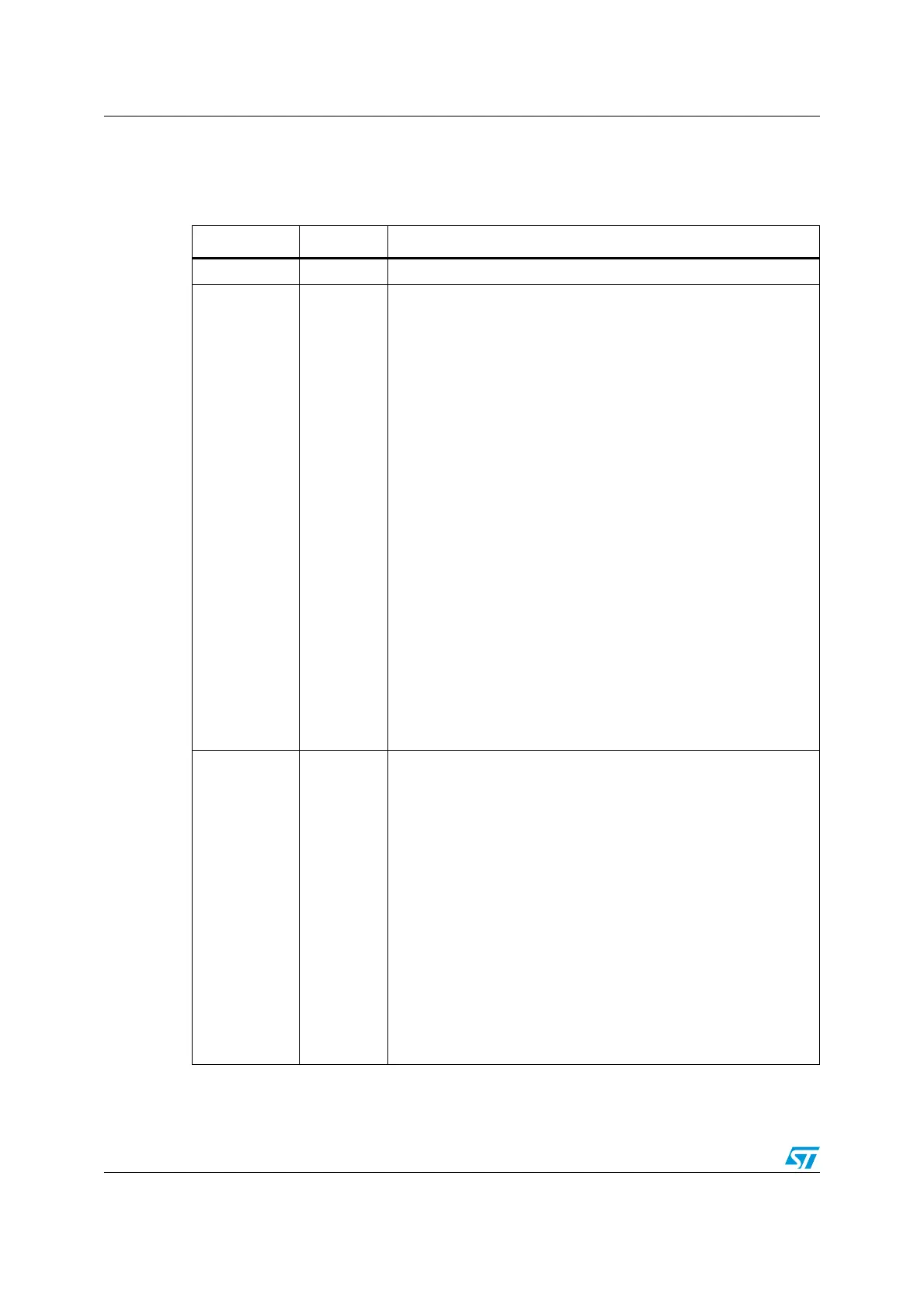

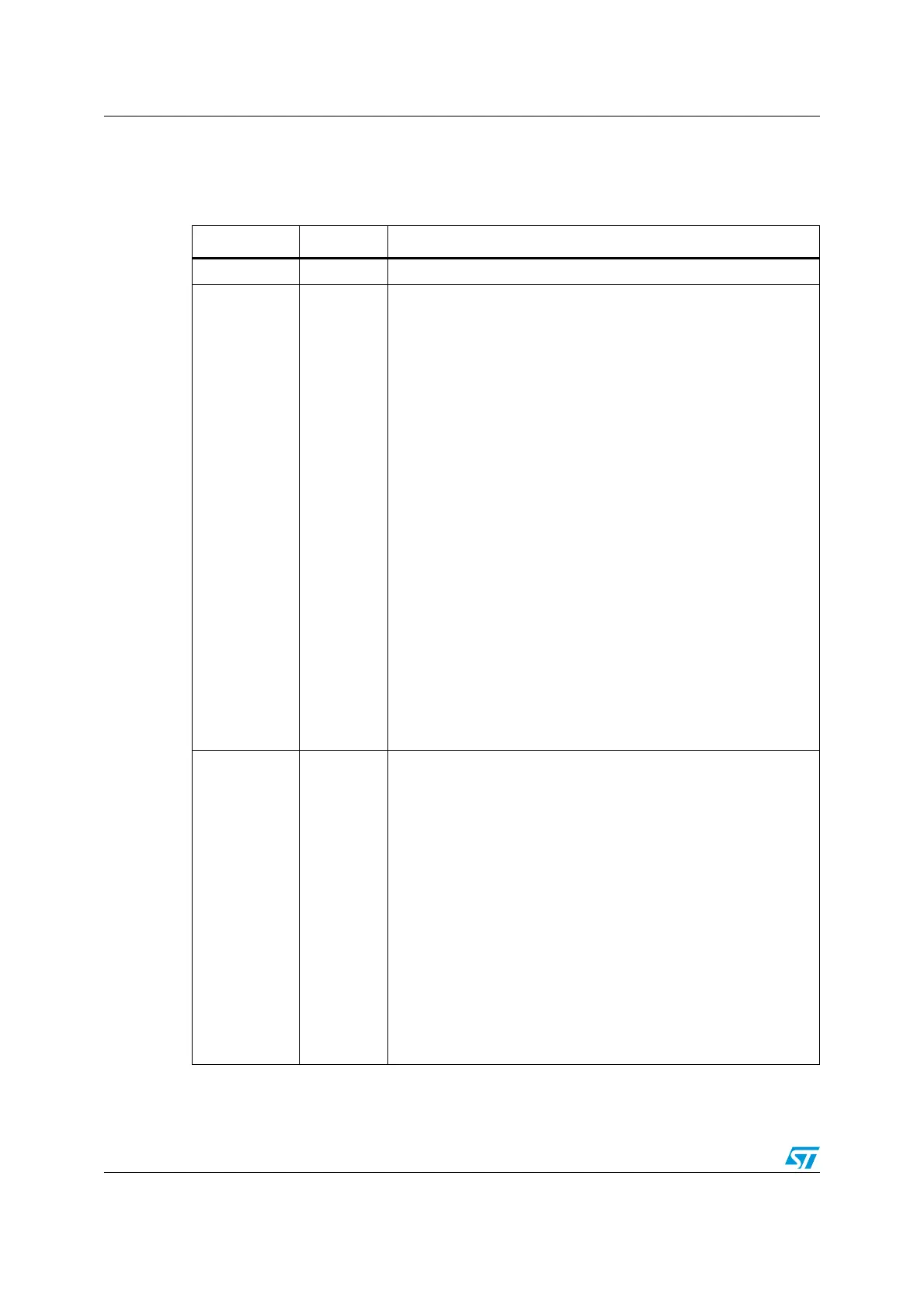

Table 240. Document revision history

Date Version Changes

15-Sep-2011 1 Initial release.

19-Oct-2012 2

Updated reference documents and added Table 1: Applicable

products on cover page.

MEMORY:

Updated Section 2.3.1: Embedded SRAM.

PWR:

Updated VDDA and VREF+ decoupling capacitor in Figure 7: Power

supply overview.

Updated case of no external battery in Section 5.1.2: Battery backup

domain.

VOSRDY bit changed to read-only in Section 5.4.3: PWR power

control/status register (PWR_CSR).

Removed VDDA in Section 5.2.3: Programmable voltage detector

(PVD) and remove VDDA in PVDO bit description (Section 5.4.3:

PWR power control/status register (PWR_CSR)).

RCC:

Updated Figure 12: Simplified diagram of the reset circuit and

minimum reset pulse duration guaranteed by pulse generator

restricted to internal reset sources.

GPIOs:

Updated Section 7.3.1: General-purpose I/O (GPIO).

19-Oct-2012

2

(continued)

DMA:

Updated direct mode description in Section 9.2: DMA main features.

Updated direct mode description in Section : Memory-to-peripheral

mode, and Section 9.3.12: FIFO/Direct mode.

Modified Stream2 /Channel 2 in Table 35: DMA1 request mapping.

Added note related to EN bit in Section 9.5.5: DMA stream x

configuration register (DMA_SxCR) (x = 0..7). Updated definition of

NDT[15:0] bits in Section 9.5.6: DMA stream x number of data

register (DMA_SxNDTR) (x = 0..7).

Updated register access in Section 9.5: DMA registers.

Interrupts:

Updated number of maskable interrupts to 82 in Section 10.1.1:

NVIC featuress.

EXTI:

Updated Section 10.2: External interrupt/event controller (EXTI)

Loading...

Loading...