RM0090 DMA controller (DMA)

Doc ID 018909 Rev 4 222/1422

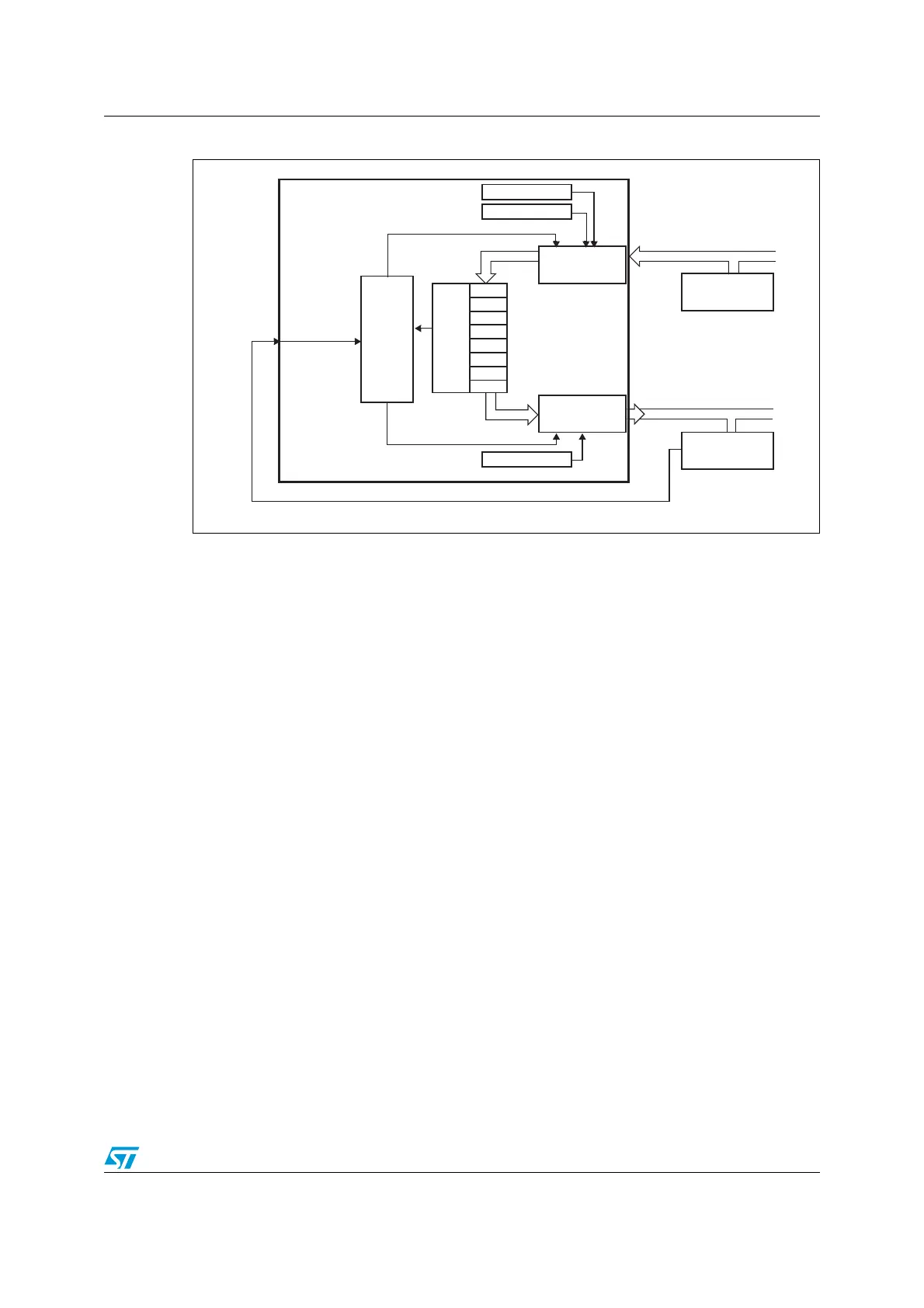

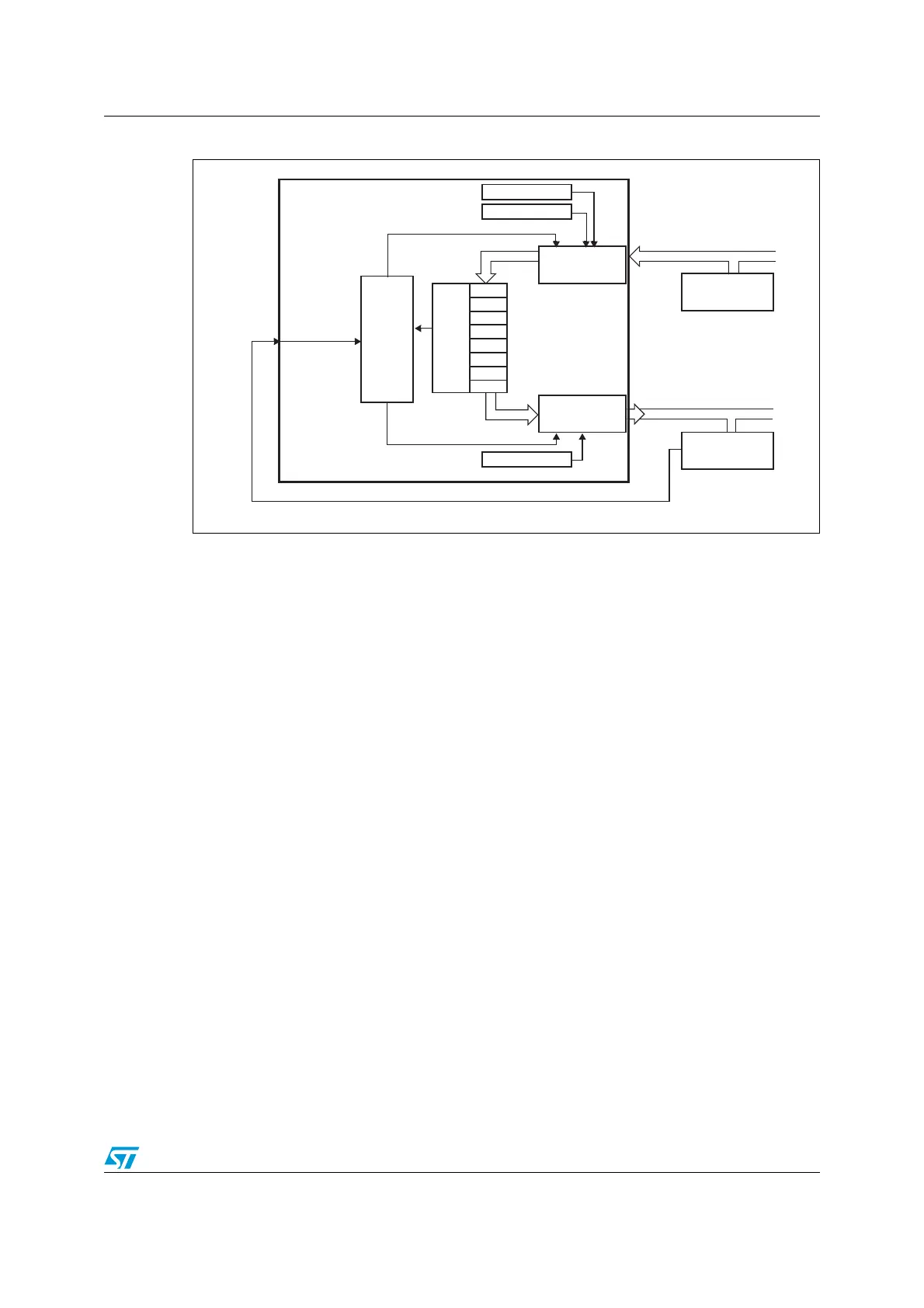

Figure 29. Memory-to-peripheral mode

1. For double-buffer mode.

Memory-to-memory mode

The DMA channels can also work without being triggered by a request from a peripheral.

This is the memory-to-memory mode, described in Figure 30.

When the stream is enabled by setting the Enable bit (EN) in the DMA_SxCR register, the

stream immediately starts to fill the FIFO up to the threshold level. When the threshold level

is reached, the FIFO contents are drained and stored into the destination.

The transfer stops once the DMA_SxNDTR register reaches zero or when the EN bit in the

DMA_SxCR register is cleared by software.

The stream has access to the AHB source or destination port only if the arbitration of the

corresponding stream is won. This arbitration is performed using the priority defined for

each stream using the PL[1:0] bits in the DMA_SxCR register.

Note: When memory-to-memory mode is used, the Circular and direct modes are not allowed.

Only the DMA2 controller is able to perform memory-to-memory transfers.

Peripheral bus

Memory bus

REQ_STREAMx

Arbiter

DMA_SxM1AR

(1)

FIFO

AHB memory

port

AHB peripheral

port

DMA_SxPAR

FIFO

level

DMA controller

DMA_SxM0AR

source

destination

Peripheral

Memory

Peripheral DMA request

ai15949

Loading...

Loading...