Ethernet (ETH): media access control (MAC) with DMA controller RM0090

911/1422 Doc ID 018909 Rev 4

MII_TXD[0] is the least significant bit, MII_TXD[3] is the most significant bit. While

MII_TX_EN is deasserted the transmit data must have no effect upon the PHY.

● MII_CRS: carrier sense is asserted by the PHY when either the transmit or receive

medium is non idle. It shall be deasserted by the PHY when both the transmit and

receive media are idle. The PHY must ensure that the MII_CS signal remains asserted

throughout the duration of a collision condition. This signal is not required to transition

synchronously with respect to the TX and RX clocks. In full duplex mode the state of

this signal is don’t care for the MAC sublayer.

● MII_COL: collision detection must be asserted by the PHY upon detection of a collision

on the medium and must remain asserted while the collision condition persists. This

signal is not required to transition synchronously with respect to the TX and RX clocks.

In full duplex mode the state of this signal is don’t care for the MAC sublayer.

● MII_RXD[3:0]: reception data is a bundle of 4 data signals driven synchronously by the

PHY and qualified (valid data) on the assertion of the MII_RX_DV signal. MII_RXD[0] is

the least significant bit, MII_RXD[3] is the most significant bit. While MII_RX_EN is

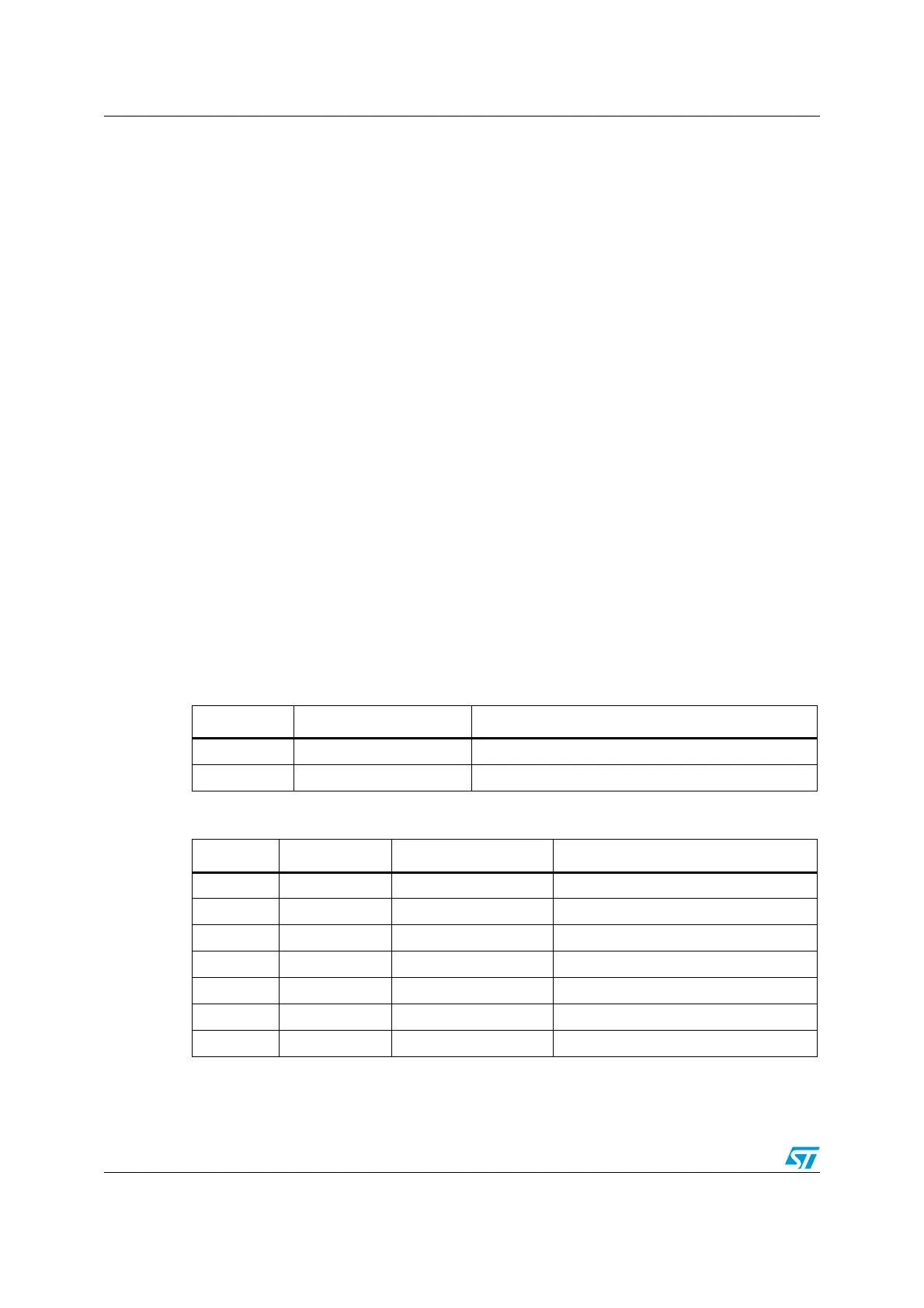

deasserted and MII_RX_ER is asserted, a specific MII_RXD[3:0] value is used to

transfer specific information from the PHY (see Tabl e 1 6 4 ).

● MII_RX_DV: receive data valid indicates that the PHY is presenting recovered and

decoded nibbles on the MII for reception. It must be asserted synchronously

(MII_RX_CLK) with the first recovered nibble of the frame and must remain asserted

through the final recovered nibble. It must be deasserted prior to the first clock cycle

that follows the final nibble. In order to receive the frame correctly, the MII_RX_DV

signal must encompass the frame, starting no later than the SFD field.

● MII_RX_ER: receive error must be asserted for one or more clock periods

(MII_RX_CLK) to indicate to the MAC sublayer that an error was detected somewhere

in the frame. This error condition must be qualified by MII_RX_DV assertion as

described in Tabl e 1 6 4 .

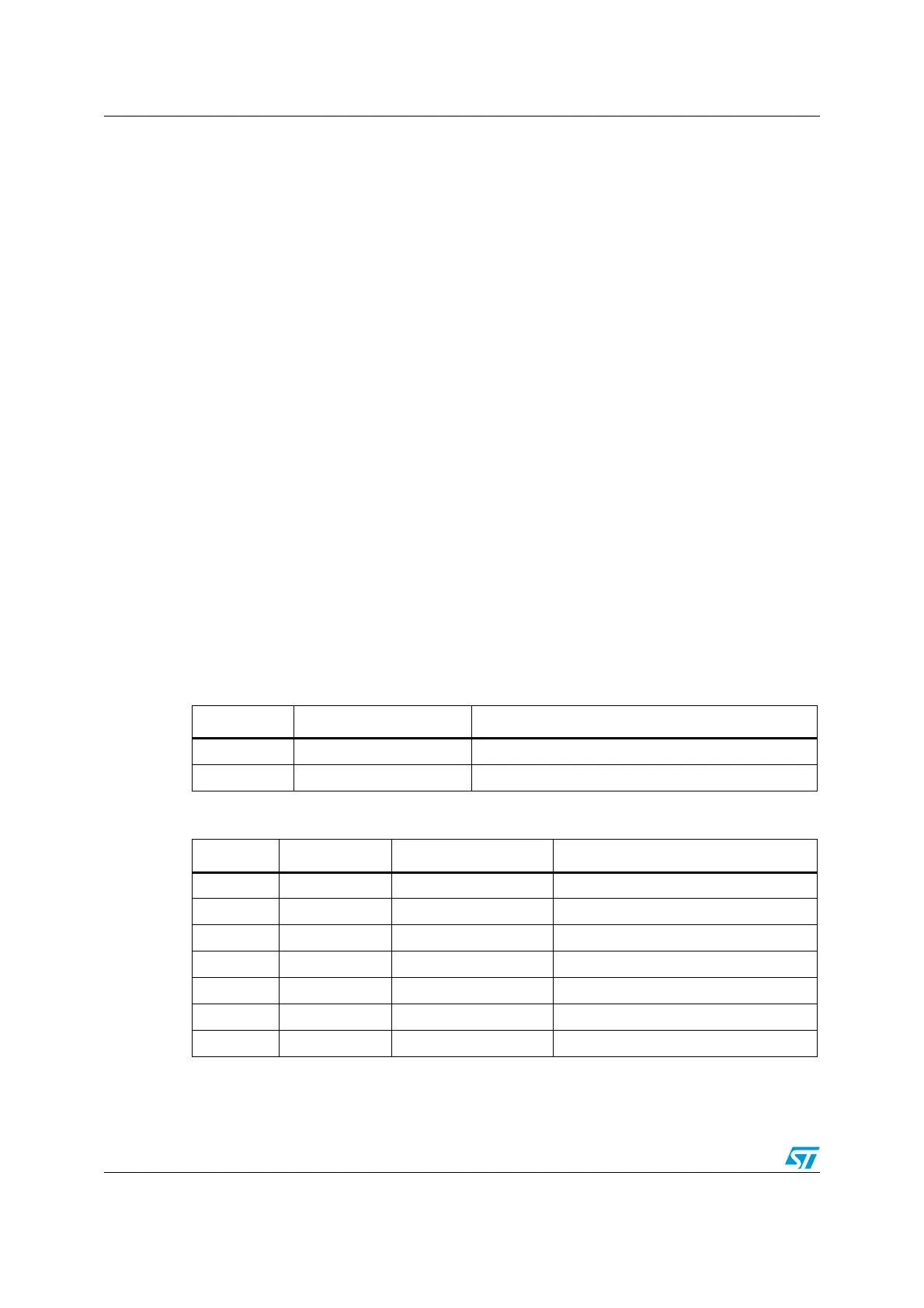

Table 163. TX interface signal encoding

MII_TX_EN MII_TXD[3:0] Description

0 0000 through 1111 Normal inter-frame

1 0000 through 1111 Normal data transmission

Table 164. RX interface signal encoding

MII_RX_DV MII_RX_ERR MII_RXD[3:0] Description

0 0 0000 through 1111 Normal inter-frame

0 1 0000 Normal inter-frame

0 1 0001 through 1101 Reserved

0 1 1110 False carrier indication

0 1 1111 Reserved

1 0 0000 through 1111 Normal data reception

1 1 0000 through 1111 Data reception with errors

Loading...

Loading...