RM0090 USB on-the-go high-speed (OTG_HS)

Doc ID 018909 Rev 4 1260/1422

Refer to Table 2 on page 52 for the register boundary addresses.

31.13 OTG_HS programming model

31.13.1 Core initialization

The application must perform the core initialization sequence. If the cable is connected

during power-up, the current mode of operation bit in the Core interrupt register (CMOD bit

in OTG_HS_GINTSTS) reflects the mode. The OTG_HS controller enters host mode when

an “A” plug is connected or peripheral mode when a “B” plug is connected.

This section explains the initialization of the OTG_HS controller after power-on. The

application must follow the initialization sequence irrespective of host or peripheral mode

operation. All core global registers are initialized according to the core’s configuration:

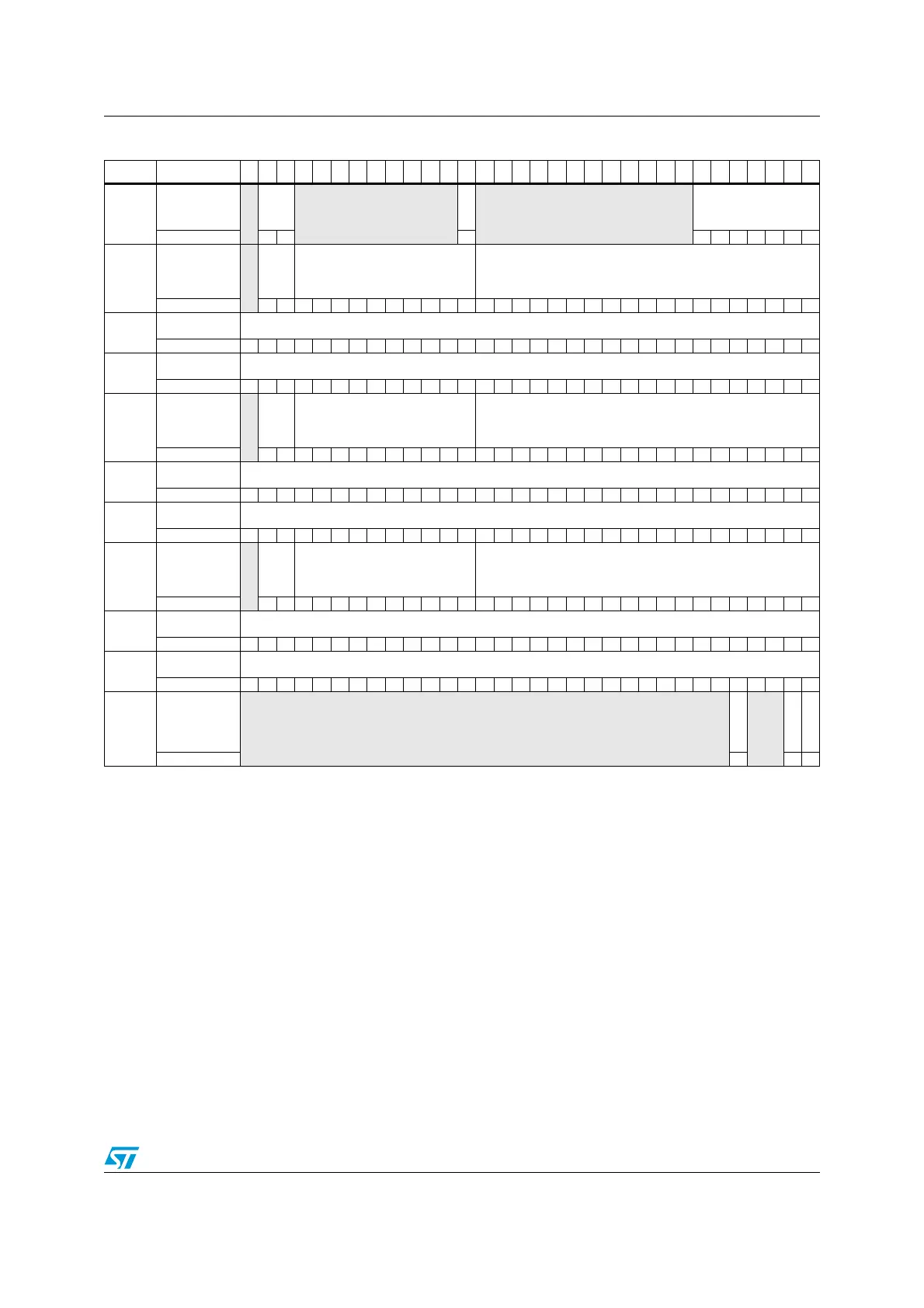

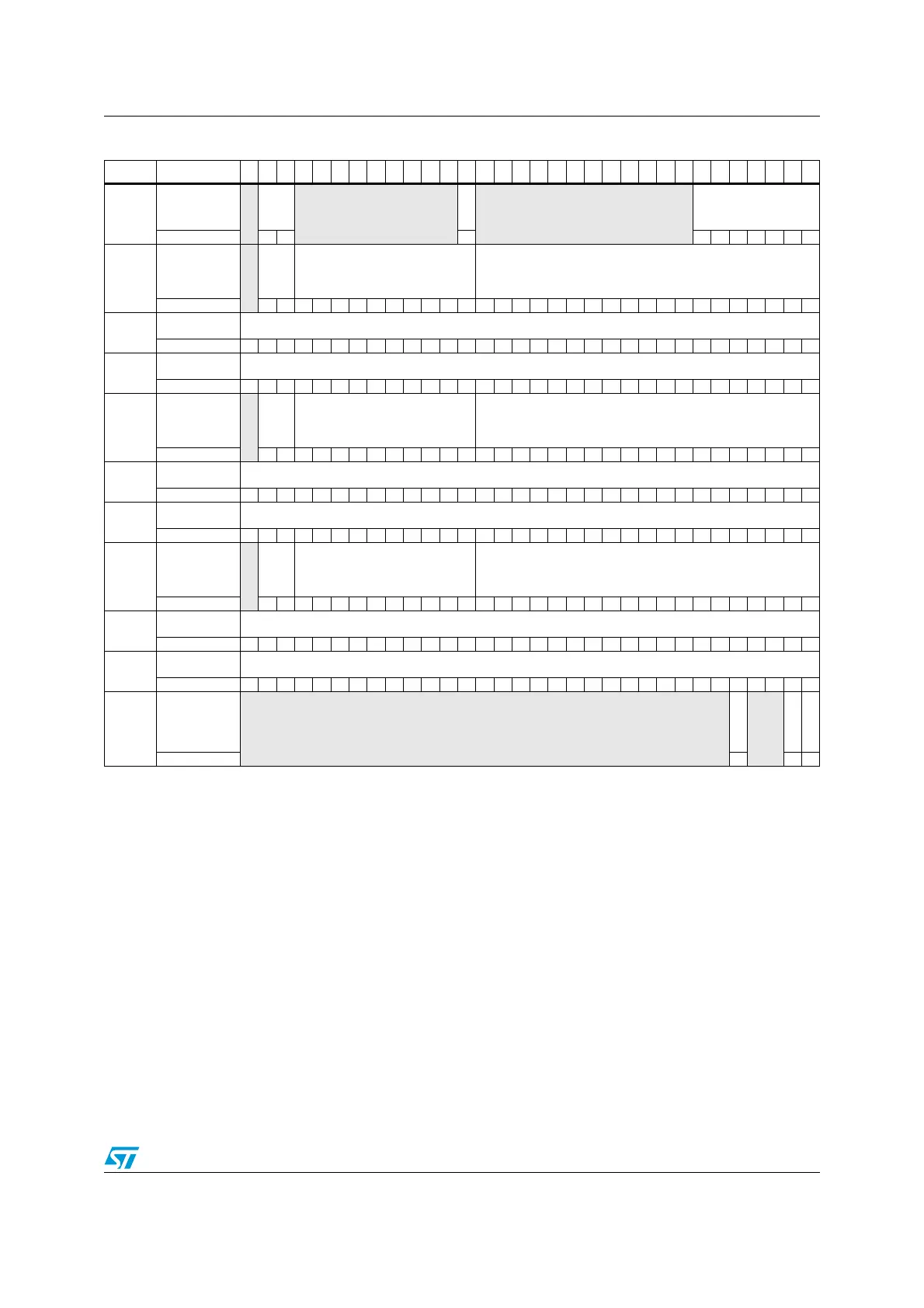

0xB10

OTG_HS_DOE

PTSIZ0

Reserved

STUP

CNT

Reserved

PKTCNT

Reserved

XFRSIZ

Reset value 00 0 0000000

0xB30

OTG_HS_DOE

PTSIZ1

Reserved

RXDPID/

STUPCNT

PKTCNT XFRSIZ

Reset value 0000000000000000000000000000000

0xB34

OTG_HS_DOE

PDMA1

DMAADDR

Reset value 00000000000000000000000000000000

0xB3C

OTG_HS_DOE

PDMAB1

DMABADDR

Reset value 00000000000000000000000000000000

0xB50

OTG_HS_DOE

PTSIZ2

Reserved

RXDPID/

STUPCNT

PKTCNT XFRSIZ

Reset value 0000000000000000000000000000000

0xB54

OTG_HS_DOE

PDMA2

DMAADDR

Reset value 00000000000000000000000000000000

0xB5C

OTG_HS_DOE

PDMAB2

DMABADDR

Reset value 00000000000000000000000000000000

0xB70

OTG_HS_DOE

PTSIZ3

Reserved

RXDPID/

STUPCNT

PKTCNT XFRSIZ

Reset value 0000000000000000000000000000000

0xB74

OTG_HS_DOE

PDMA3

DMAADDR

Reset value 00000000000000000000000000000000

0xB7C

OTG_HS_DOE

PDMAB3

DMABADDR

Reset value 00000000000000000000000000000000

0xE00

OTG_HS_PCG

CCTL

Reserved

PHYSUSP

Reserved

GATEHCLK

STPPCLK

Reset value

Table 184. OTG_HS register map and reset values (continued)

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Loading...

Loading...