Hash processor (HASH) RM0090

601/1422 Doc ID 018909 Rev 4

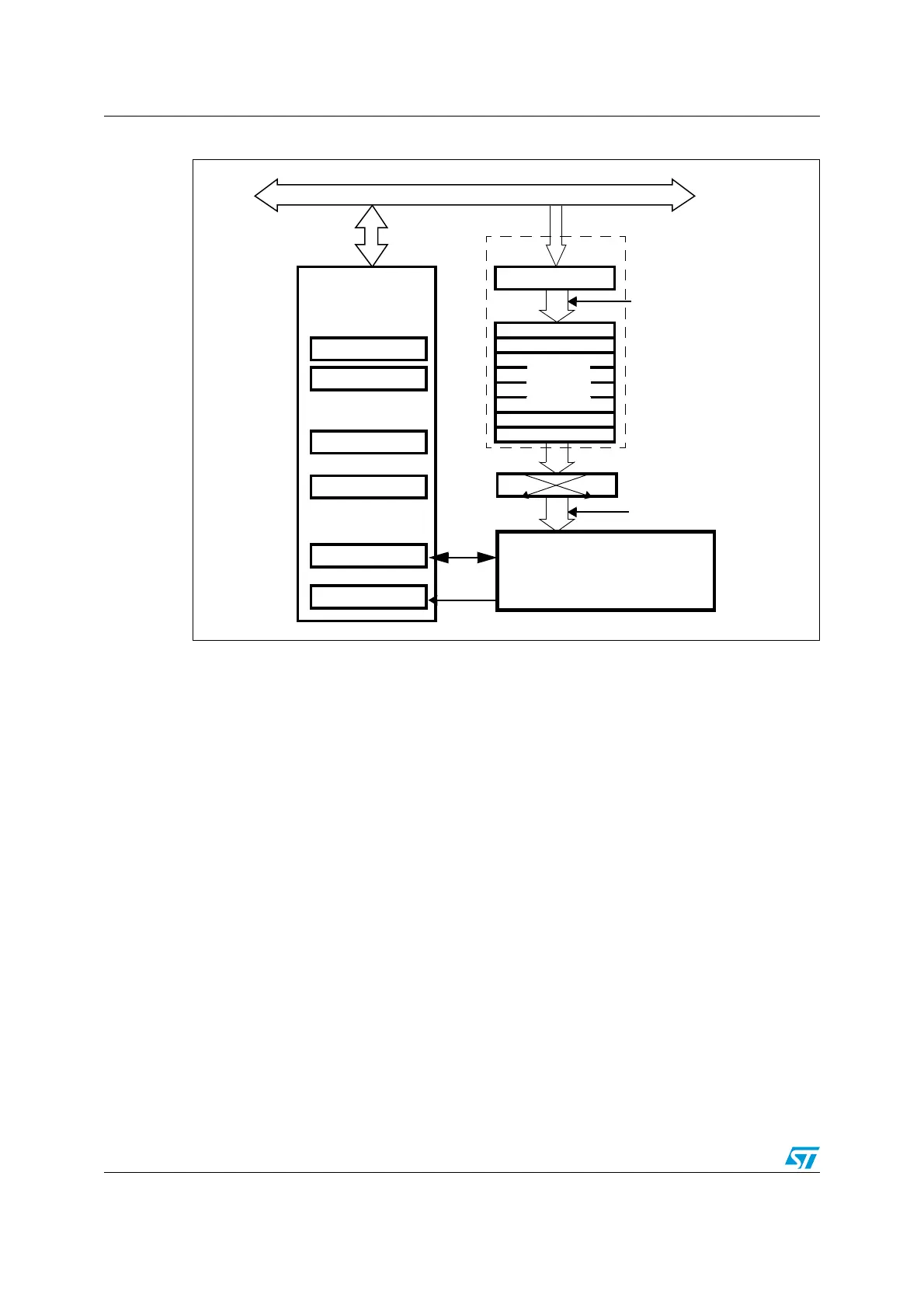

Figure 219. Block diagram for STM32F42xxx and STM32F43xxx

The FIPS PUB 180-2 standard and the IETF RFC 1321 publication specify the SHA-1, SHA-

224 and SHA-256 and MD5 secure hash algorithms, respectively, for computing a

condensed representation of a message or data file. When a message of any length below

2

64

bits is provided on input, the SHA-1, SHA-224 and SHA-256 and MD5 produce

respective a 160-bit, 224 bit, 256 bit and 128-bit output string, respectively, called a

message digest. The message digest can then be processed with a digital signature

algorithm in order to generate or verify the signature for the message. Signing the message

digest rather than the message often improves the efficiency of the process because the

message digest is usually much smaller in size than the message. The verifier of a digital

signature has to use the same hash algorithm as the one used by the creator of the digital

signature.

The SHA-1, SHA-224 and SHA-256 and MD5 are qualified as “secure” because it is

computationally infeasible to find a message that corresponds to a given message digest, or

to find two different messages that produce the same message digest. Any change to a

message in transit will, with very high probability, result in a different message digest, and

the signature will fail to verify. For more detail on the SHA-1 or SHA-224 and SHA-256

algorithm, please refer to the FIPS PUB 180-2 (Federal Information Processing Standards

Publication 180-2), 2002 august 1.

The current implementation of this standard works with little-endian input data convention.

For example, the C string “abc” must be represented in memory as the 24-bit hexadecimal

value 0x434241.

A message or data file to be processed by the hash processor should be considered a bit

string. The length of the message is the number of bits in the message (the empty message

32-bit AHB2 bus

Hash / HMAC

SHA-1, SHA-224, SHA-256 and MD5

HASH_DIN

swa ppin g

16 × 32-bit

IN FIFO

HASH_CR

HASH_H0...H7

HASH_CSR0..53

context

digest

HASH_IMR

HASH_SR

Interrupt registers

Control register

Context swapping

Message digest

processor core

HASH_ST R

Start register

IN FIFO full

write into HASH_DIN

Control and status

registers

Data

register

or write DCAL bit to 1

or 1 complete block

or DCAL written to 1

IN buffer

transferred by the DMA

MS30442V1

Loading...

Loading...