RM0090 Debug support (DBG)

Doc ID 018909 Rev 4 1386/1422

Refer to the Cortex™-M4Fr0p1 TRM for a detailed description of DPACC and APACC

registers.

The packet request is always followed by the turnaround time (default 1 bit) where neither

the host nor target drive the line.

The ACK Response must be followed by a turnaround time only if it is a READ transaction or

if a WAIT or FAULT acknowledge has been received.

The DATA transfer must be followed by a turnaround time only if it is a READ transaction.

33.8.3 SW-DP state machine (reset, idle states, ID code)

The State Machine of the SW-DP has an internal ID code which identifies the SW-DP. It

follows the JEP-106 standard. This ID code is the default ARM one and is set to

0x2BA01477 (corresponding to Cortex™-M4F r0p1).

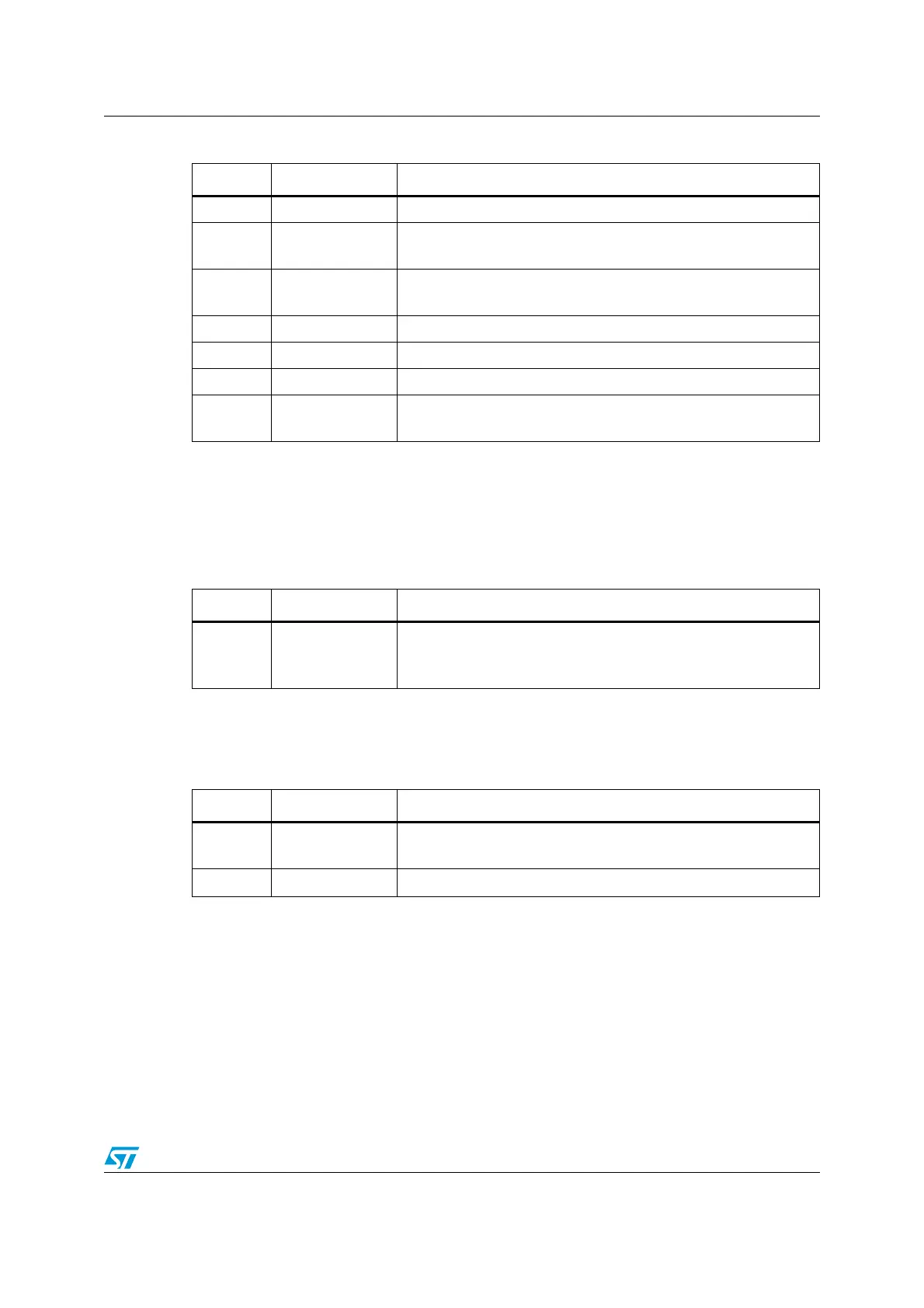

Table 227. Packet request (8-bits)

Bit Name Description

0 Start Must be “1”

1 APnDP

0: DP Access

1: AP Access

2RnW

0: Write Request

1: Read Request

4:3 A(3:2) Address field of the DP or AP registers (refer to Table 226)

5 Parity Single bit parity of preceding bits

6Stop 0

7Park

Not driven by the host. Must be read as “1” by the target

because of the pull-up

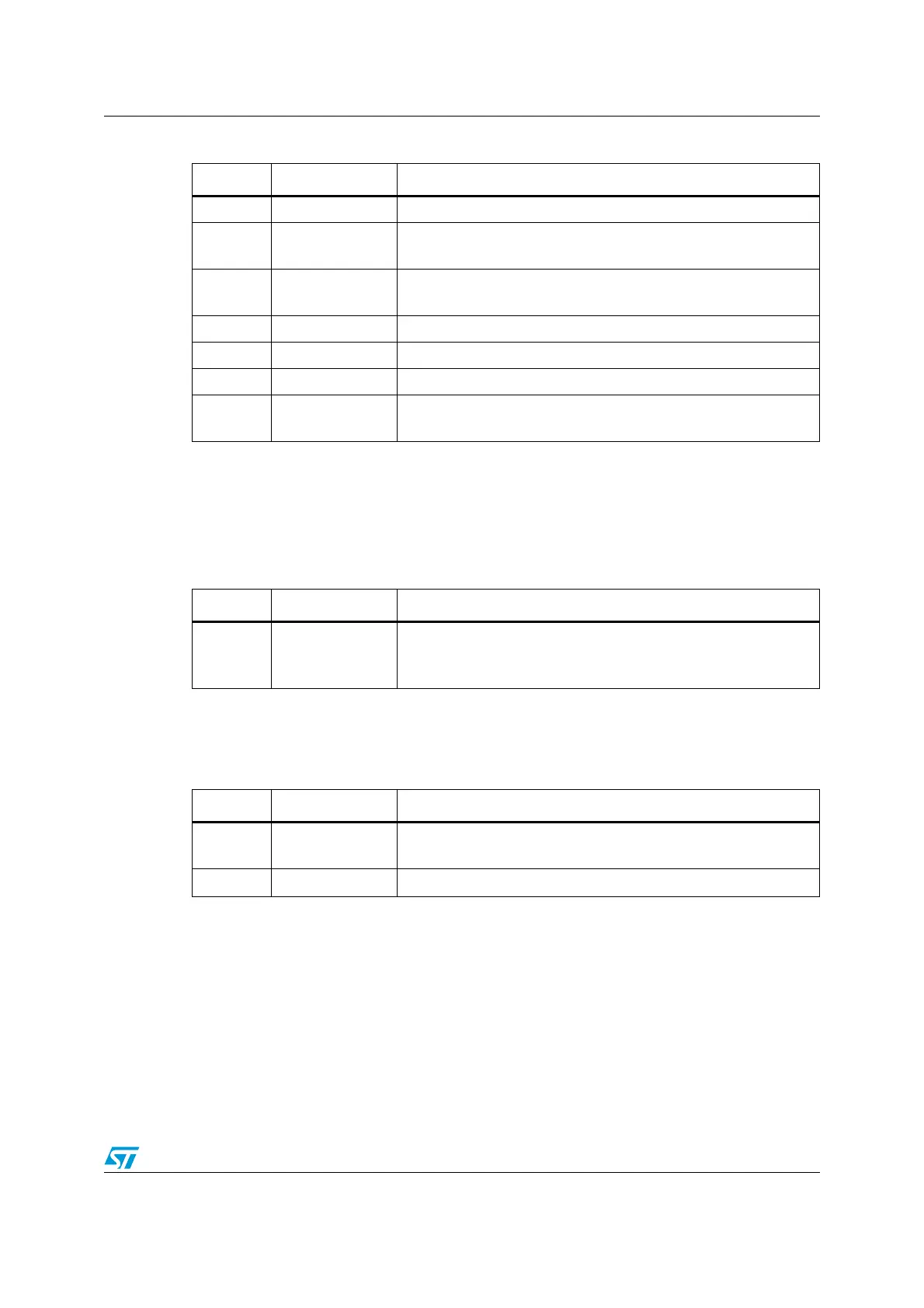

Table 228. ACK response (3 bits)

Bit Name Description

0..2

ACK

001: FAULT

010: WAIT

100: OK

Table 229. DATA transfer (33 bits)

Bit Name Description

0..31

WDATA or

RDATA

Write or Read data

32

Parity

Single parity of the 32 data bits

Loading...

Loading...