RM0090 Universal synchronous asynchronous receiver transmitter (USART)

Doc ID 018909 Rev 4 764/1422

26.3.5 USART receiver tolerance to clock deviation

The USART asynchronous receiver works correctly only if the total clock system deviation is

smaller than the USART receiver’s tolerance. The causes which contribute to the total

deviation are:

● DTRA: Deviation due to the transmitter error (which also includes the deviation of the

transmitter’s local oscillator)

● DQUANT: Error due to the baud rate quantization of the receiver

● DREC: Deviation of the receiver’s local oscillator

● DTCL: Deviation due to the transmission line (generally due to the transceivers which

can introduce an asymmetry between the low-to-high transition timing and the high-to-

low transition timing)

DTRA + DQUANT + DREC + DTCL < USART receiver’s tolerance

The USART receiver’s tolerance to properly receive data is equal to the maximum tolerated

deviation and depends on the following choices:

● 10- or 11-bit character length defined by the M bit in the USART_CR1 register

● oversampling by 8 or 16 defined by the OVER8 bit in the USART_CR1 register

● use of fractional baud rate or not

● use of 1 bit or 3 bits to sample the data, depending on the value of the ONEBIT bit in

the USART_CR3 register

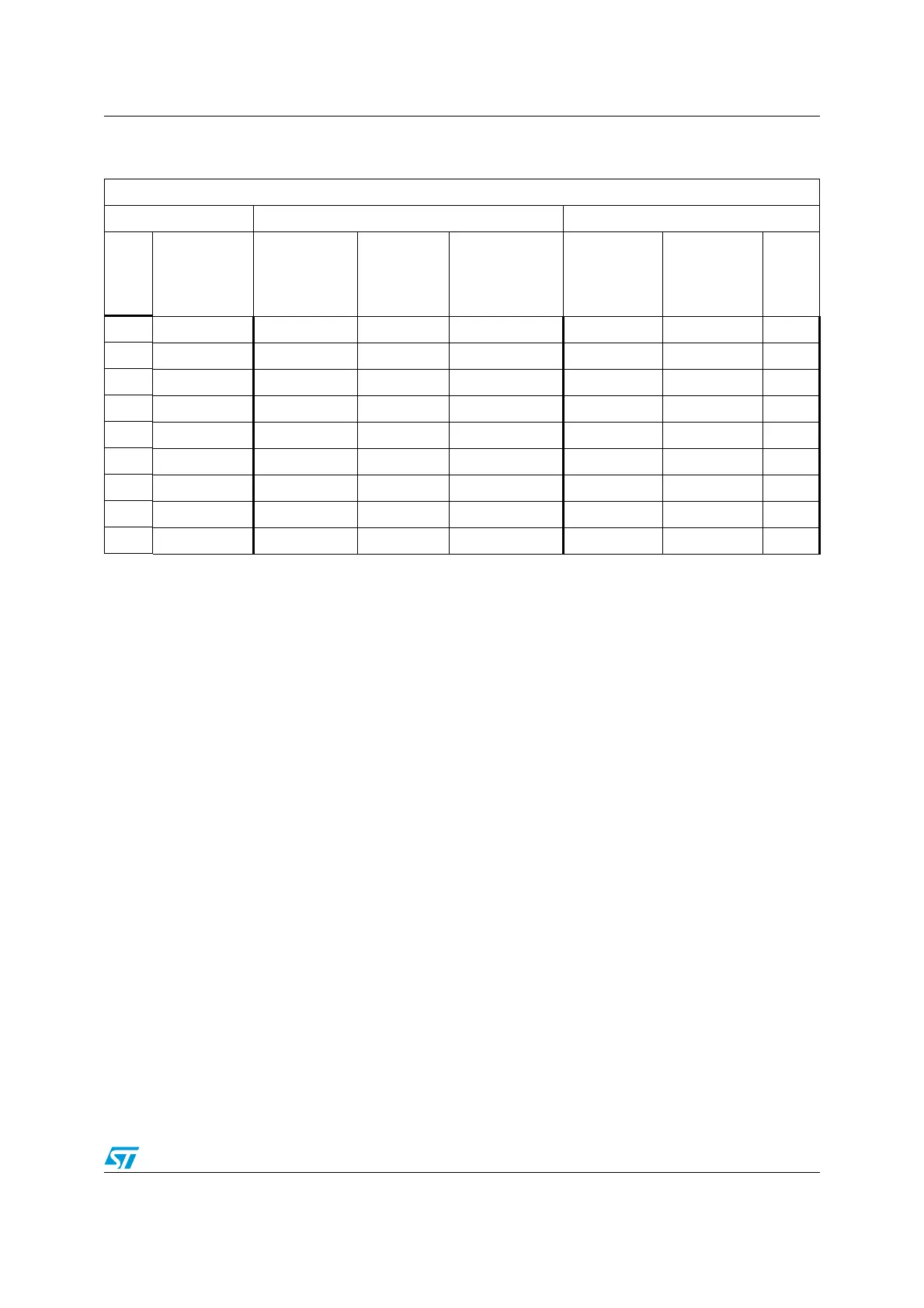

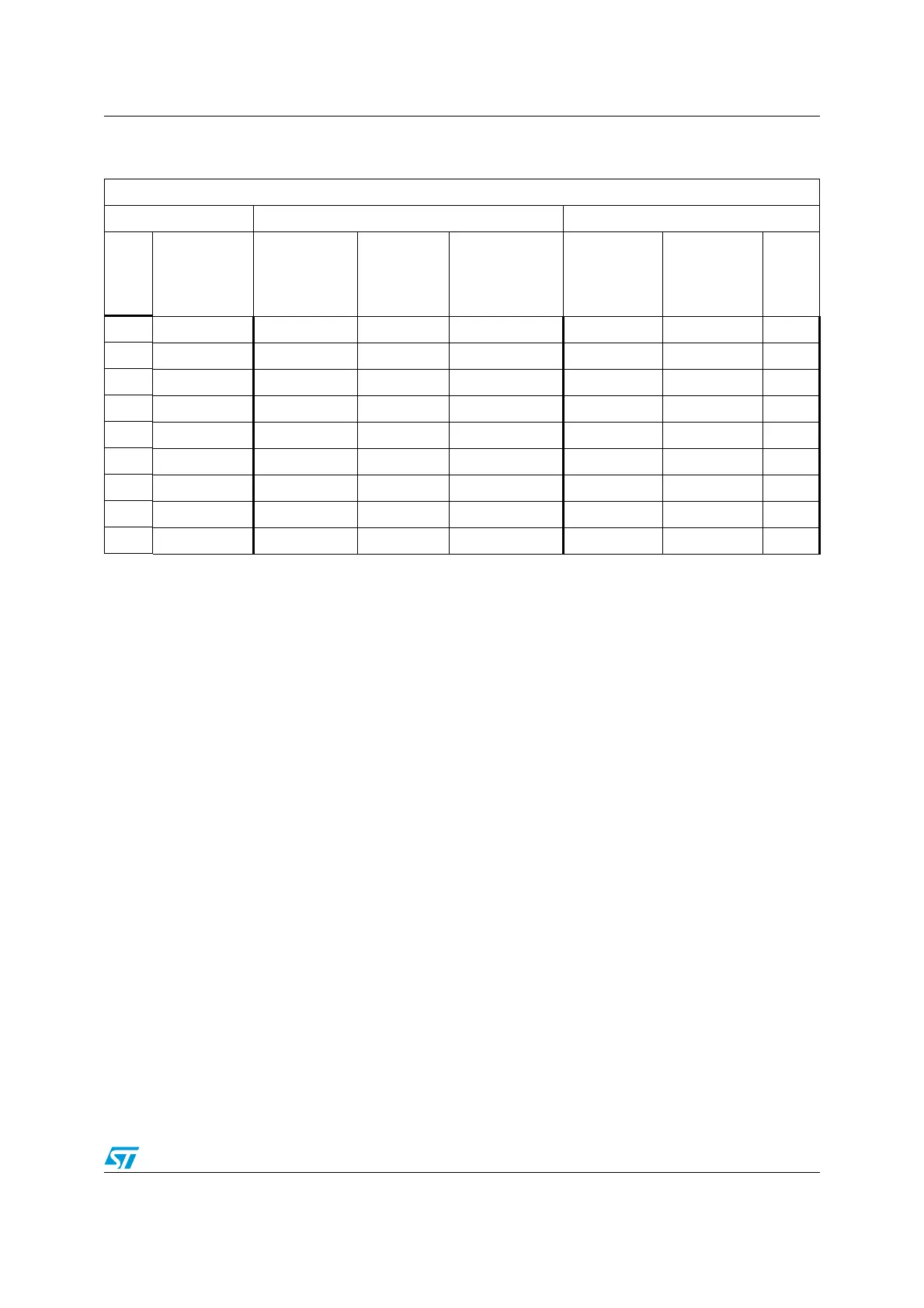

10. 921.6 KBps 913.043 KBps 5.75 0.93 923.076 KBps 11.375 0.93

11. 1.792 MBps 1.826 MBps 2.875 1.9 1.787Mbps 5.875 0.27

12. 1.8432 MBps 1.826 MBps 2.875 0.93 1.826 MBps 5.75 0.93

13. 3.584 MBps 3.5 MBps 1.5 2.34 3.652 MBps 2.875 1.9

14. 3.6864 MBps 3.82 MBps 1.375 3.57 3.652 MBps 2.875 0.93

15. 7.168 MBps N.A N.A N.A 7 MBps 1.5 2.34

16. 7.3728 MBps N.A N.A N.A 7.636 MBps 1.375 3.57

18. 9 MBps N.A N.A N.A 9.333 MBps 1.125 3.7

20. 10.5 MBps N.A N.A N.A 10.5 MBps 1 0

1. The lower the CPU clock the lower the accuracy for a particular baud rate. The upper limit of the achievable baud rate can

be fixed with these data.

2. Only USART1 and USART6 are clocked with PCLK2. Other USARTs are clocked with PCLK1. Refer to the device

datasheets for the maximum values for PCLK1 and PCLK2.

Table 117. Error calculation for programmed baud rates at f

PCLK

= 42 MHz or f

PCLK

= 84 MHz,

oversampling by 8

(1)(2)

(continued)

Oversampling by 8 (OVER8=1)

Baud rate f

PCLK

= 42 MHz f

PCLK

= 84 MHz

S.No Desired Actual

Value

programmed

in the baud

rate register

% Error =

(Calculated -

Desired)B.Rate

/Desired B.Rate

Actual

Value

programmed

in the baud

rate register

% Error

Loading...

Loading...