RM0090 USB on-the-go high-speed (OTG_HS)

Doc ID 018909 Rev 4 1180/1422

Host-mode CSR map

These registers must be programmed every time the core changes to host mode.

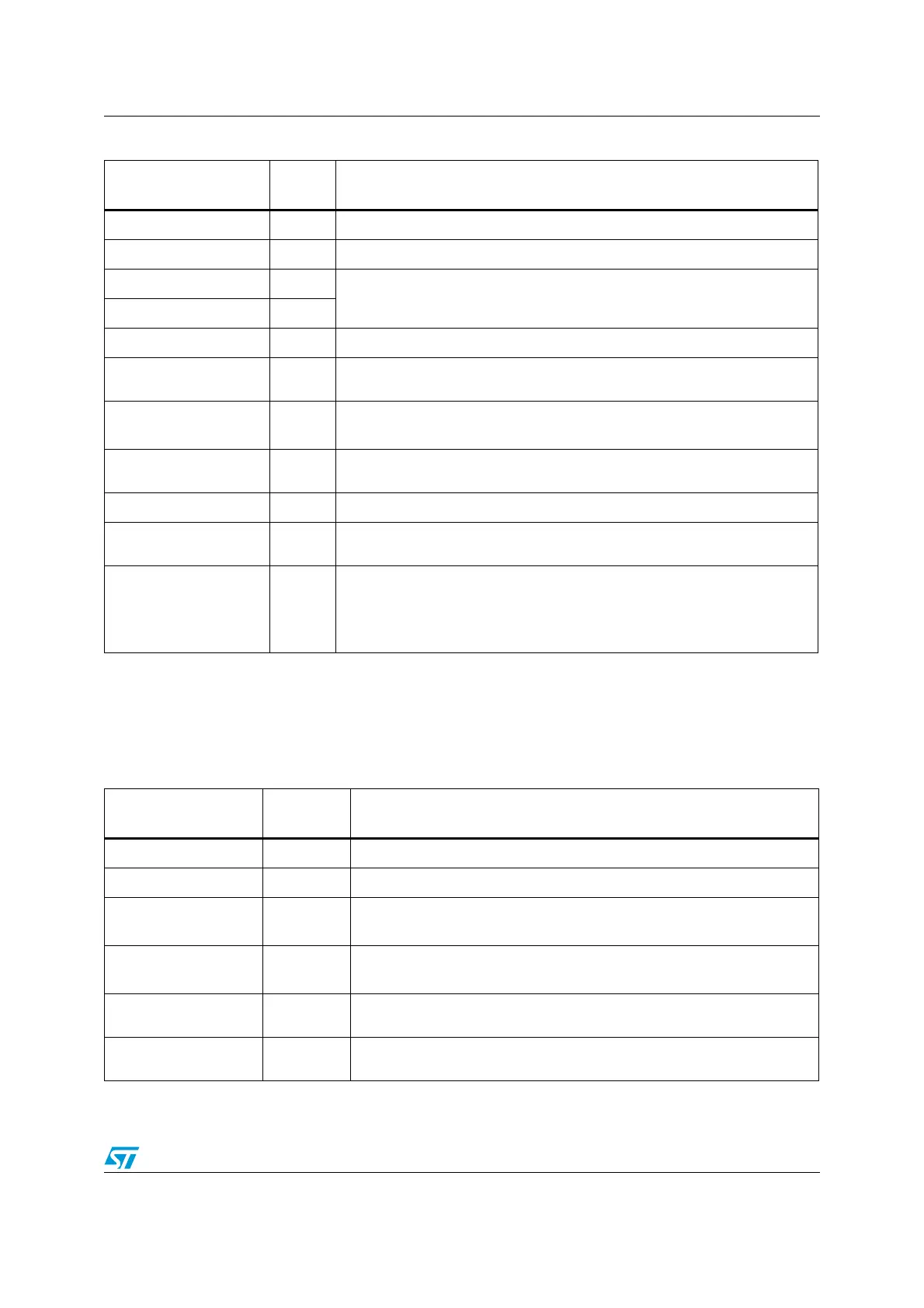

OTG_HS_GINTSTS 0x014 OTG_HS core interrupt register (OTG_HS_GINTSTS) on page 1194

OTG_HS_GINTMSK 0x018 OTG_HS interrupt mask register (OTG_HS_GINTMSK) on page 1198

OTG_HS_GRXSTSR 0x01C

OTG_HS Receive status debug read/OTG status read and pop registers

(OTG_HS_GRXSTSR/OTG_HS_GRXSTSP) on page 1201

OTG_HS_GRXSTSP 0x020

OTG_HS_GRXFSIZ 0x024 OTG_HS Receive FIFO size register (OTG_HS_GRXFSIZ) on page 1202

OTG_HS_GNPTXFSIZ/

OTG_HS_TX0FSIZ

0x028

OTG_HS nonperiodic transmit FIFO size/Endpoint 0 transmit FIFO size

register (OTG_HS_GNPTXFSIZ/OTG_HS_TX0FSIZ) on page 1203

OTG_HS_GNPTXSTS 0x02C

OTG_HS nonperiodic transmit FIFO/queue status register

(OTG_HS_GNPTXSTS) on page 1203

OTG_HS_GCCFG 0x038

OTG_HS general core configuration register (OTG_HS_GCCFG) on

page 1206

OTG_HS_CID 0x03C OTG_HS core ID register (OTG_HS_CID) on page 1207

OTG_HS_HPTXFSIZ 0x100

OTG_HS Host periodic transmit FIFO size register (OTG_HS_HPTXFSIZ) on

page 1207

OTG_HS_DIEPTXFx

0x104

0x124

...

0x13C

OTG_HS device IN endpoint transmit FIFO size register

(OTG_HS_DIEPTXFx) (x = 1..7, where x is the FIFO_number) on page 1207

Table 178. Core global control and status registers (CSRs) (continued)

Acronym

Address

offset

Register name

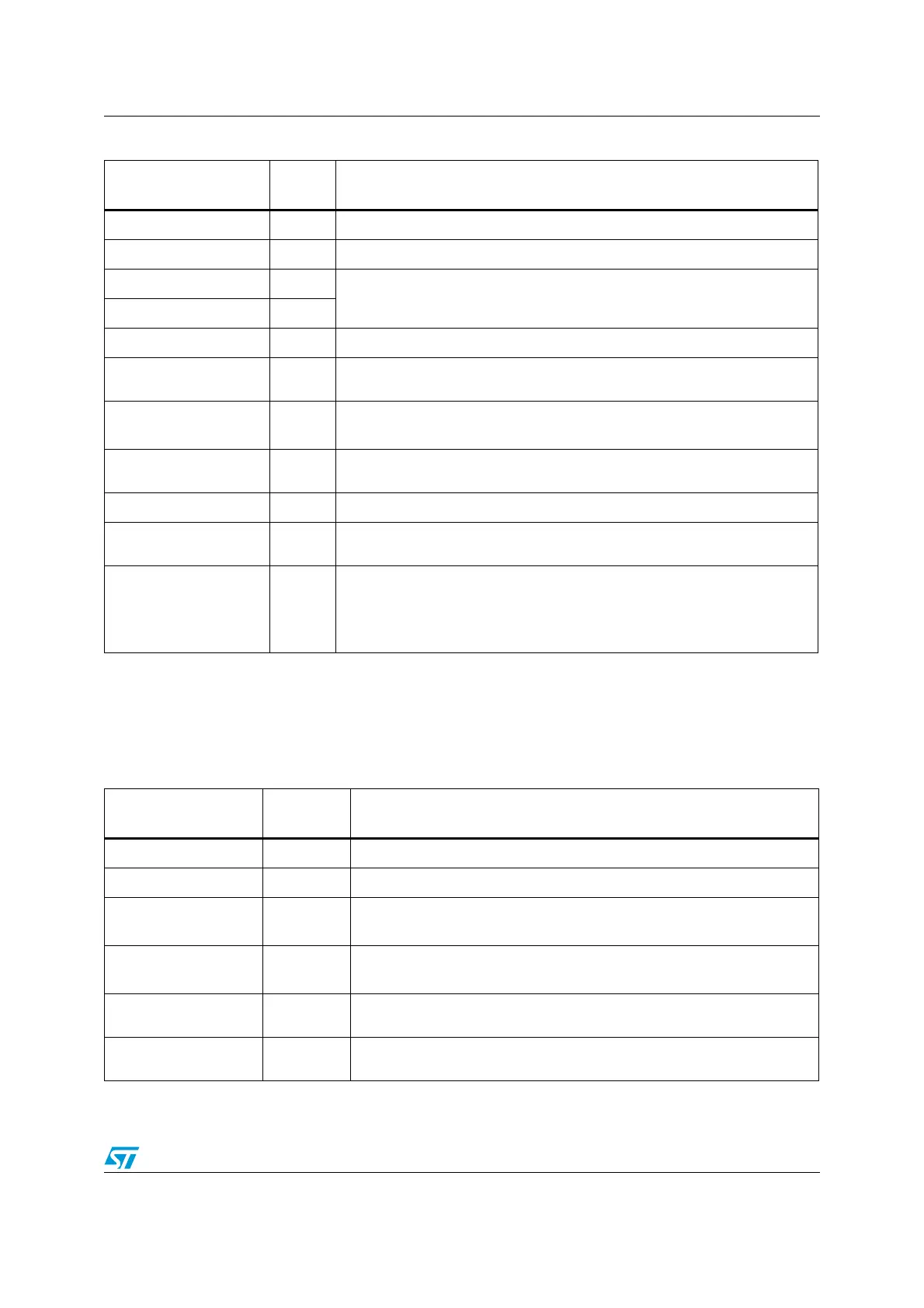

Table 179. Host-mode control and status registers (CSRs)

Acronym

Offset

address

Register name

OTG_HS_HCFG 0x400 OTG_HS host configuration register (OTG_HS_HCFG) on page 1208

OTG_HS_HFIR 0x404 OTG_HS Host frame interval register (OTG_HS_HFIR) on page 1209

OTG_HS_HFNUM 0x408

OTG_HS host frame number/frame time remaining register

(OTG_HS_HFNUM) on page 1209

OTG_HS_HPTXSTS 0x410

OTG_HS_Host periodic transmit FIFO/queue status register

(OTG_HS_HPTXSTS) on page 1210

OTG_HS_HAINT 0x414

OTG_HS Host all channels interrupt register (OTG_HS_HAINT) on

page 1211

OTG_HS_HAINTMSK 0x418

OTG_HS host all channels interrupt mask register (OTG_HS_HAINTMSK)

on page 1211

Loading...

Loading...