Hash processor (HASH) RM0090

619/1422 Doc ID 018909 Rev 4

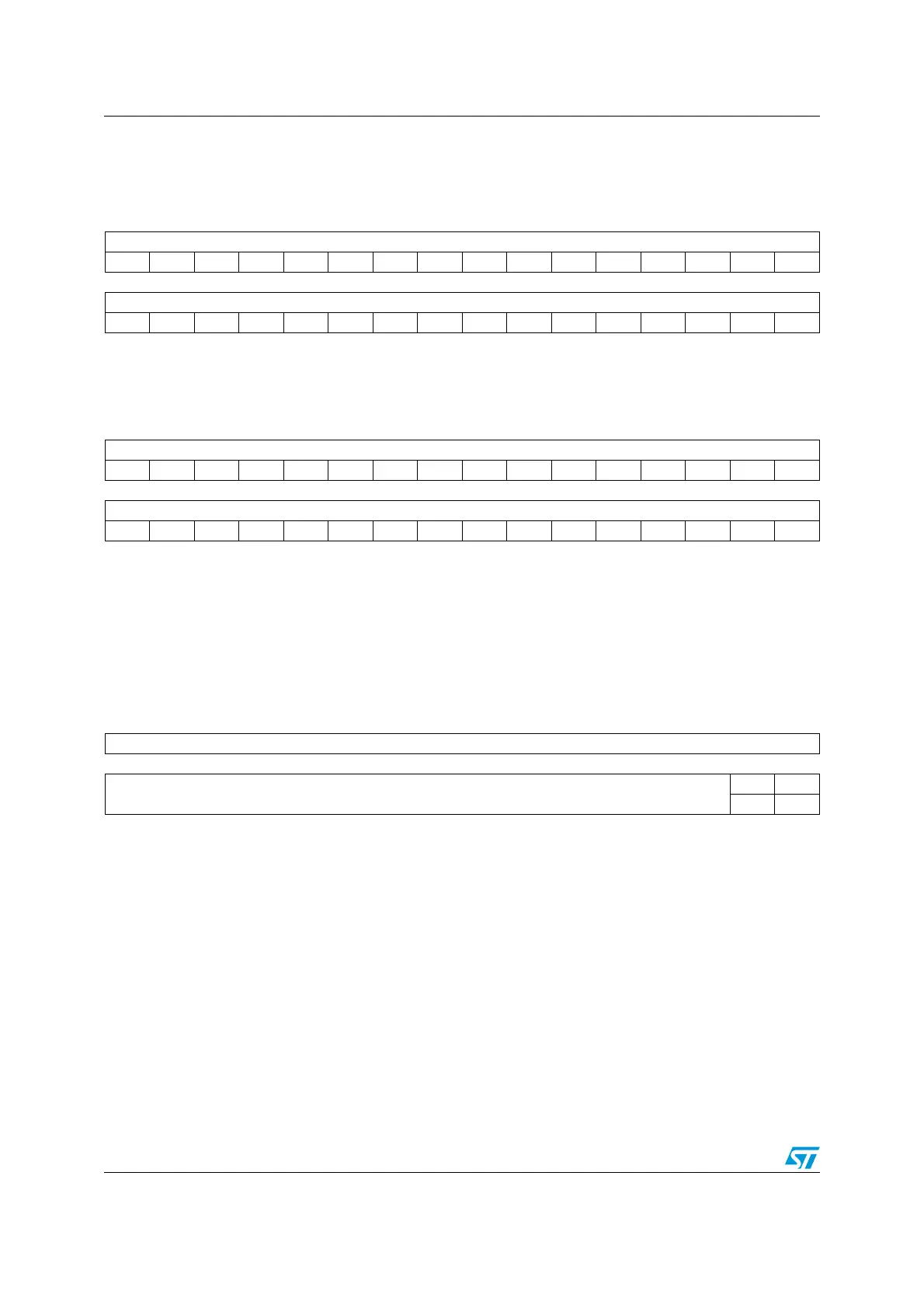

HASH_HR6

Address offset: 0x328

HASH_HR7

Address offset: 0x32C

Note: When starting a digest computation for a new bit stream (by writing the INIT bit to 1), these

registers assume their reset values.

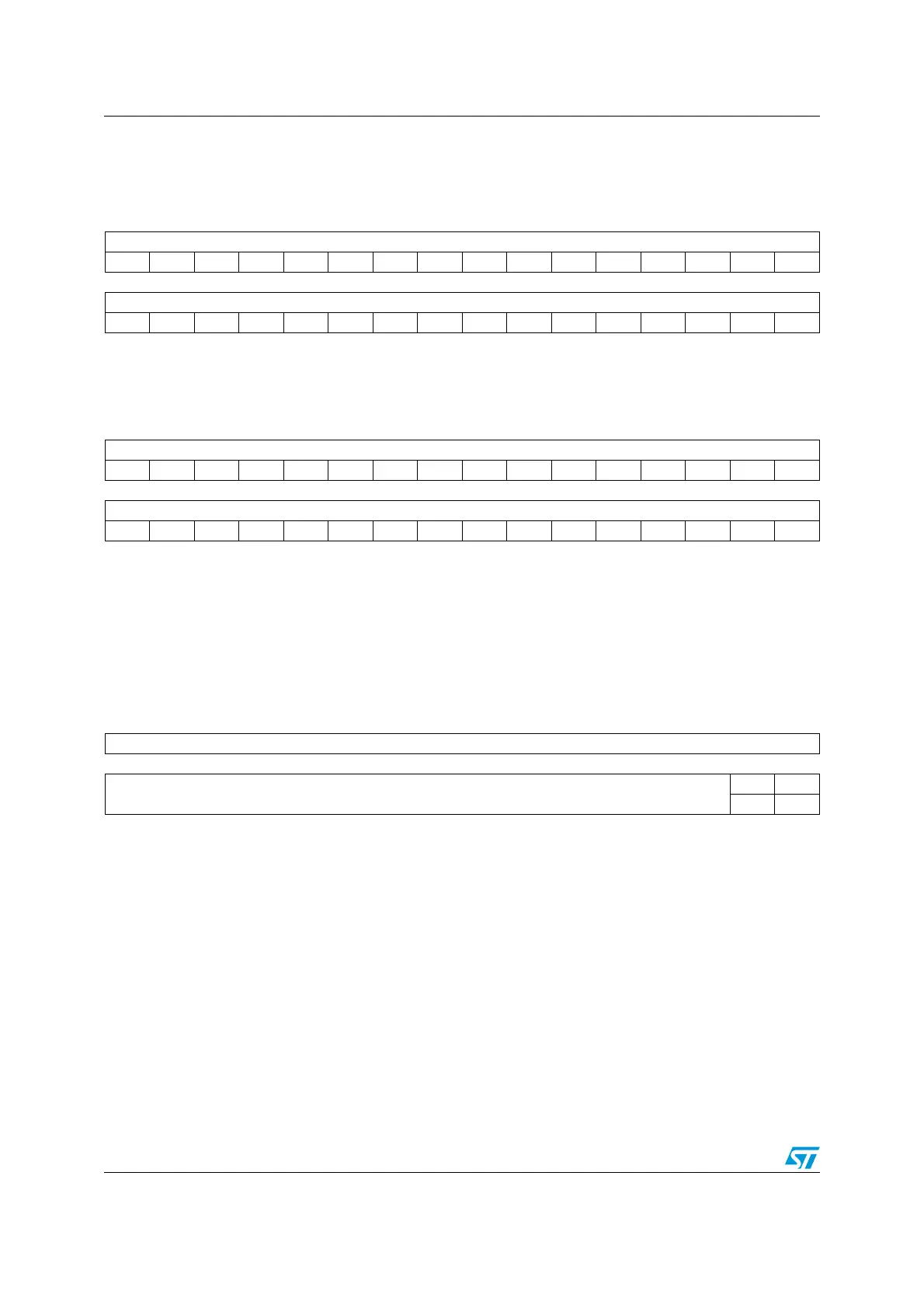

22.4.6 HASH interrupt enable register (HASH_IMR)

Address offset: 0x20

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

H6

rrrrrrrrrrrrrrrr

1514131211109876543210

H6

rrrrrrrrrrrrrrrr

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

H7

rrrrrrrrrrrrrrrr

1514131211109876543210

H7

rrrrrrrrrrrrrrrr

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

DCIE DINIE

rw rw

Bits 31:2 Reserved, forced by hardware to 0.

Bit 1 DCIE: Digest calculation completion interrupt enable

0: Digest calculation completion interrupt disabled

1: Digest calculation completion interrupt enabled.

Bit 0 DINIE: Data input interrupt enable

0: Data input interrupt disabled

1: Data input interrupt enabled

Loading...

Loading...