RM0090 DMA controller (DMA)

Doc ID 018909 Rev 4 218/1422

After an event, the peripheral sends a request signal to the DMA controller. The DMA

controller serves the request depending on the channel priorities. As soon as the DMA

controller accesses the peripheral, an Acknowledge signal is sent to the peripheral by the

DMA controller. The peripheral releases its request as soon as it gets the Acknowledge

signal from the DMA controller. Once the request has been deasserted by the peripheral,

the DMA controller releases the Acknowledge signal. If there are more requests, the

peripheral can initiate the next transaction.

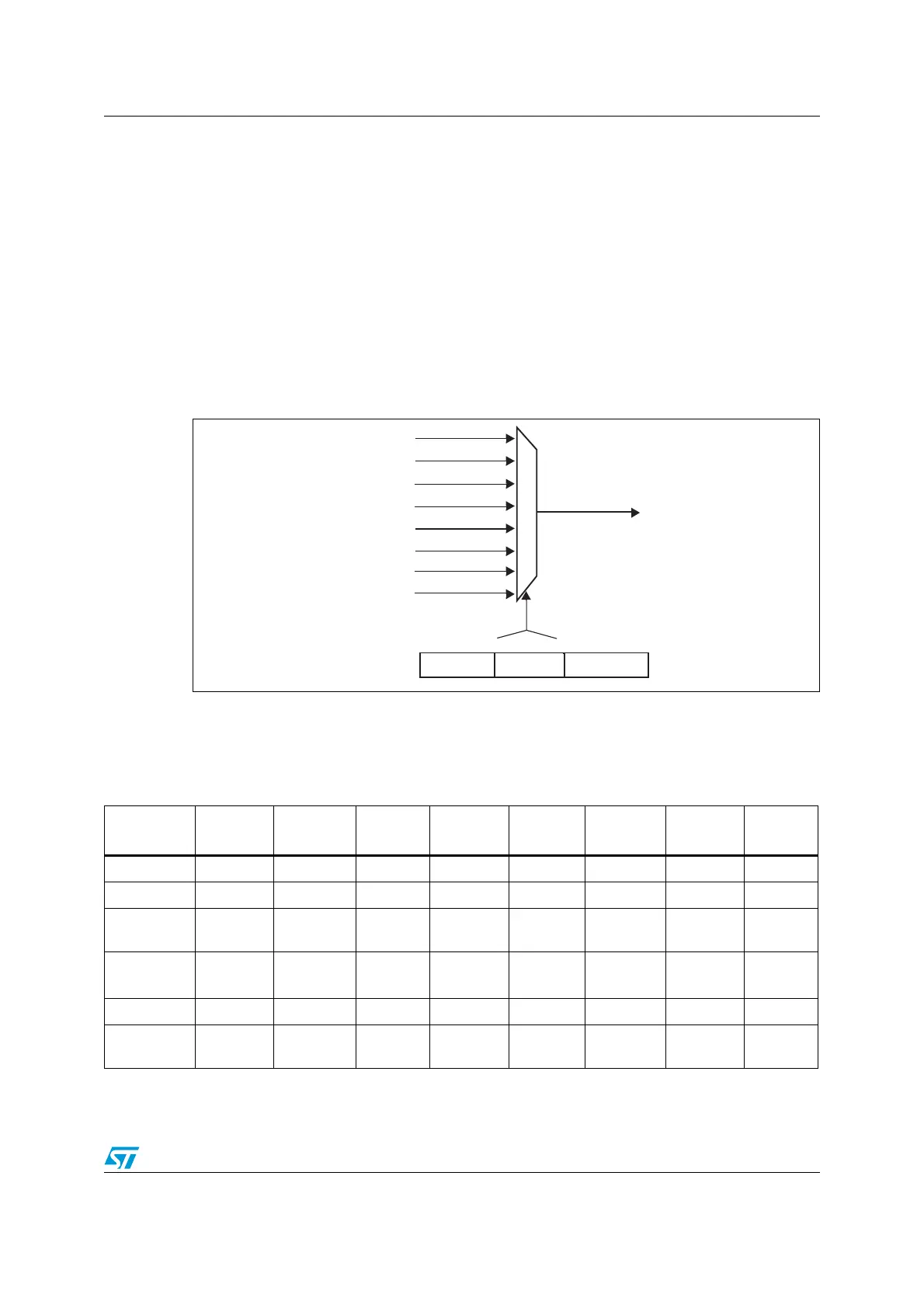

9.3.3 Channel selection

Each stream is associated with a DMA request that can be selected out of 8 possible

channel requests. The selection is controlled by the CHSEL[2:0] bits in the DMA_SxCR

register.

Figure 27. Channel selection

The 8 requests from the peripherals (TIM, ADC, SPI, I2C, etc.) are independently connected

to each channel and their connection depends on the product implementation.

Tabl e 3 5 and Ta bl e 36 give examples of DMA request mappings.

REQ_STREAMx

REQ_STRx_CH7

REQ_STRx_CH6

REQ_STRx_CH5

REQ_STRx_CH4

REQ_STRx_CH3

REQ_STRx_CH2

REQ_STRx_CH1

REQ_STRx_CH0

CHSEL[2:0]

312927 0

DMA_SxCR

ai15947

Table 35. DMA1 request mapping

Peripheral

requests

Stream 0 Stream 1 Stream 2 Stream 3 Stream 4 Stream 5 Stream 6 Stream 7

Channel 0

SPI3_RX SPI3_RX SPI2_RX SPI2_TX SPI3_TX SPI3_TX

Channel 1

I2C1_RX

TIM7_UP TIM7_UP

I2C1_RX I2C1_TX I2C1_TX

Channel 2

TIM4_CH1

I2S3_EXT_

RX

TIM4_CH2

I2S2_EXT_

TX

I2S3_EXT_

TX

TIM4_UP TIM4_CH3

Channel 3

I2S3_EXT_

RX

TIM2_UP

TIM2_CH3

I2C3_RX

I2S2_EXT_

RX

I2C3_TX TIM2_CH1

TIM2_CH2

TIM2_CH4

TIM2_UP

TIM2_CH4

Channel 4 UART5_RX USART3_RX UART4_RX USART3_TX UART4_TX

USART2_RX USART2_TX UART5_TX

Channel 5 UART8_TX

(1)

UART7_TX

(1)

TIM3_CH4

TIM3_UP

UART7_RX

(1)

TIM3_CH1

TIM3_TRIG

TIM3_CH2

UART8_RX

(1)

TIM3_CH3

Loading...

Loading...