System configuration controller (SYSCFG) RM0090

211/1422 Doc ID 018909 Rev 4

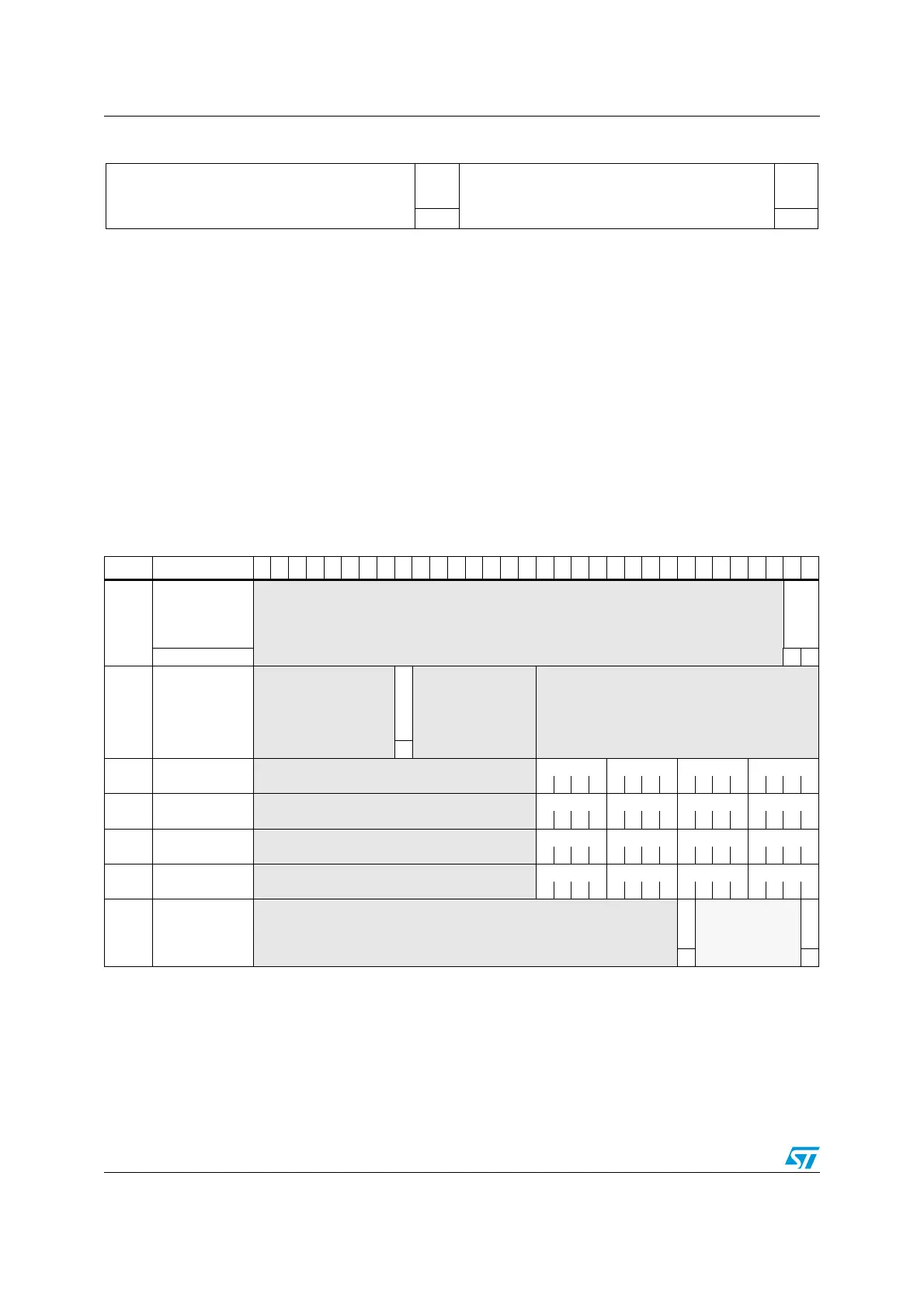

8.2.9 SYSCFG register maps

The following table gives the SYSCFG register map and the reset values.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

READY

Reserved

CMP_

PD

r rw

Bits 31:9 Reserved, must be kept at reset value.

Bit 8 READY: Compensation cell ready flag

0: I/O compensation cell not ready

1: O compensation cell ready

Bits 7:2 Reserved, must be kept at reset value.

Bit 0 CMP_PD: Compensation cell power-down

0: I/O compensation cell power-down mode

1: I/O compensation cell enabled

Table 33. SYSCFG register map and reset values STM32F405xx/07xx and STM32F415xx/17xx

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00

SYSCFG_MEMRM

Reserved

MEM_MODE

Reset value xx

0x04

SYSCFG_PMC

Reserved

MII_RMII_SEL

Reserved Reserved

Reset value 0

0x08

SYSCFG_EXTICR1

Reserved

EXTI3[3:0] EXTI2[3:0] EXTI1[3:0] EXTI0[3:0]

Reset value 0000000000000000

0x0C

SYSCFG_EXTICR2

Reserved

EXTI7[3:0] EXTI6[3:0] EXTI5[3:0] EXTI4[3:0]

Reset value 0000000000000000

0x10

SYSCFG_EXTICR3

Reserved

EXTI11[3:0] EXTI10[3:0] EXTI9[3:0] EXTI8[3:0]

Reset value 0000000000000000

0x14

SYSCFG_EXTICR4

Reserved

EXTI15[3:0] EXTI14[3:0] EXTI13[3:0] EXTI12[3:0]

Reset value 0000000000000000

0x20

SYSCFG_CMPCR

Reserved

READY

Reserved

CMP_PD

Reset value 00

Loading...

Loading...