Maintenance Object Repair Procedures

555-233-123

10-1430 Issue 4 May 2002

Processor Cache Audit (#896)

This nondestructive audit checks the state of the Cache Parity bit maintained by

the RISC CPU. If this bit is set, there may be problems with either the CPU, the

Instruction, or Data Cache. An indication of bad cache parity won’t itself mean that

the system won’t operate, but minor to severe performance degradation may be

present. For example, a single bad bit in either cache could cause this bit to be

set. If the faulty word is seldom accessed, the impact will be small. If the bit is

accessed frequently, there could be serious problems with much, or all, of the

cache (stuck data bit) with the only direct indication again being the cache parity

error or cache test error.

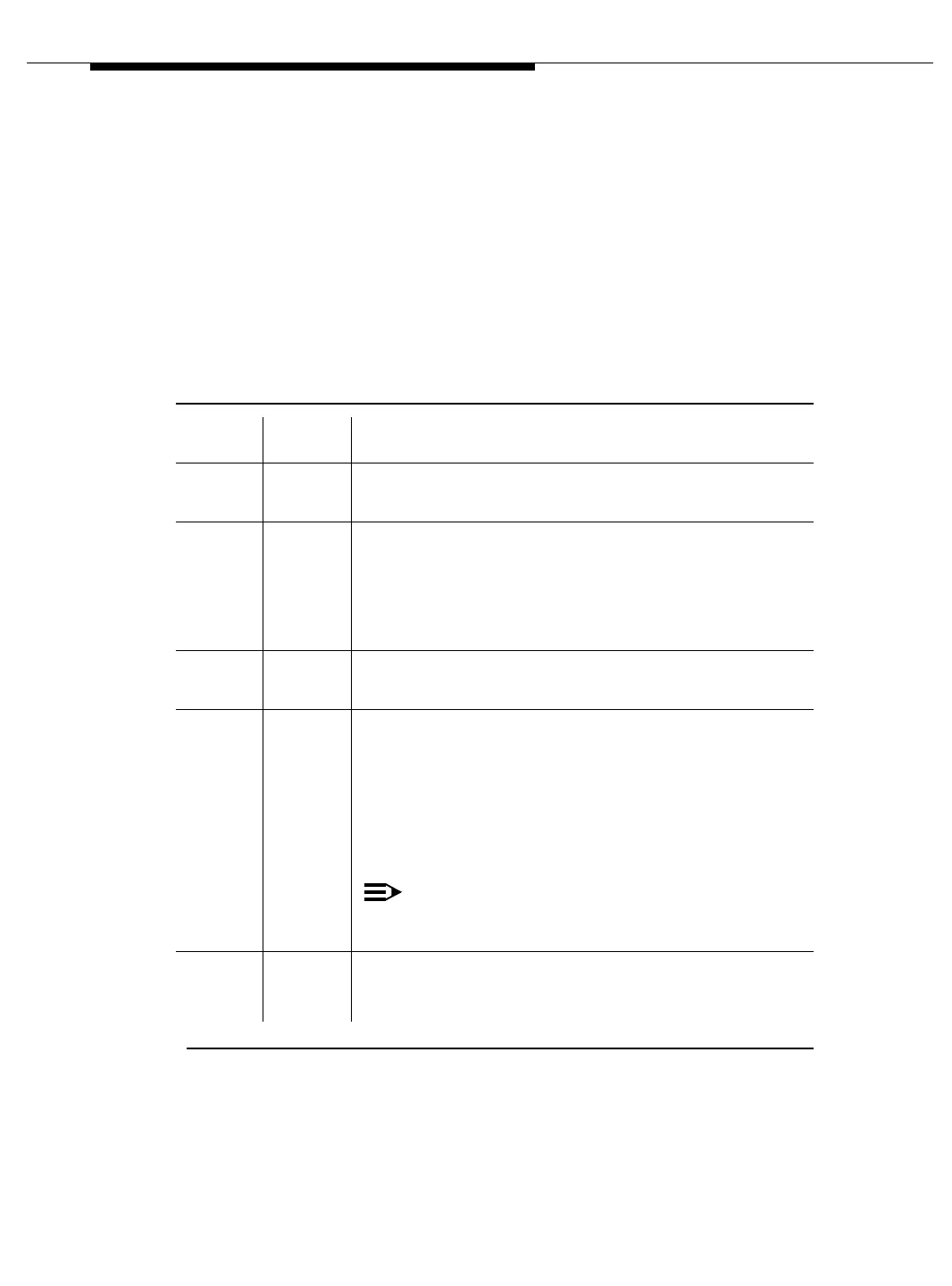

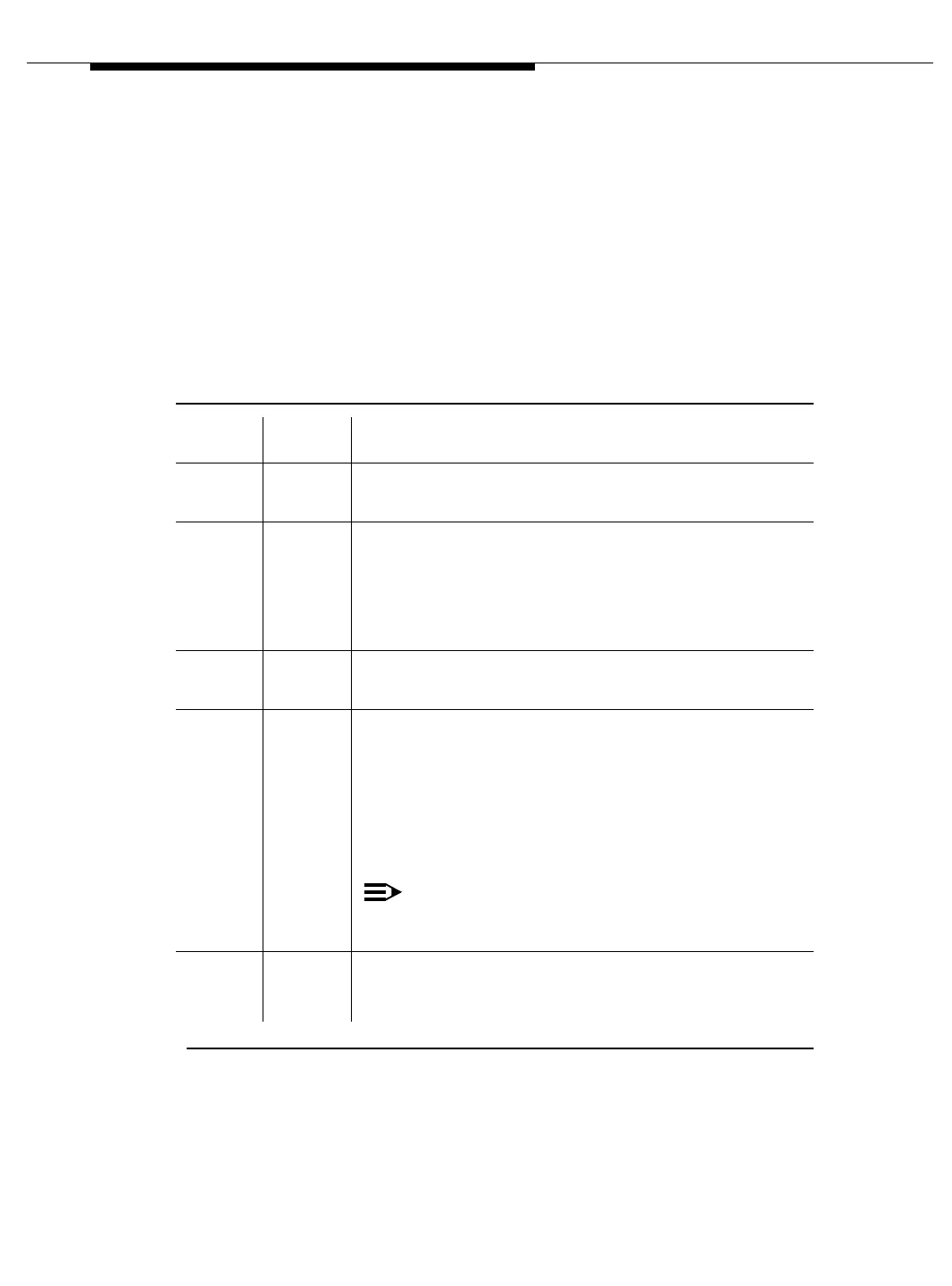

Table 10-541. Test #896 Processor Cache Audit

Error

Code

Te s t

Result Description/Recommendation

100 ABORT The test did not complete within the allowable time period.

1. Retry the command.

1029 2014

2015 2016

2017 2018

2020 2022

2024 2025

2051

ABORT Refer to STBY-SPE Maintenance documentation for a

description of these error codes.

2500 ABORT Internal system error

1. Retry the command.

FAIL The Cache Parity Error bit is set, there may be problems with

either the CPU or the Instruction or Data Cache.

1. Retry the command.

2. If the test continues to fail, run test processor a|b long.

3. If the Processor Cache test (#895) or the Processor Cache

Audit (#896) fails, replace the Processor circuit pack.

NOTE:

If you replace the Processor circuit pack, you need

to obtain a new license file.

PASS The Processor has not detected any parity errors in the

Instruction and Data Caches since the last time this audit was

run.

Continued on next page

Loading...

Loading...