MPC5604B/C Microcontroller Reference Manual, Rev. 8

94 Freescale Semiconductor

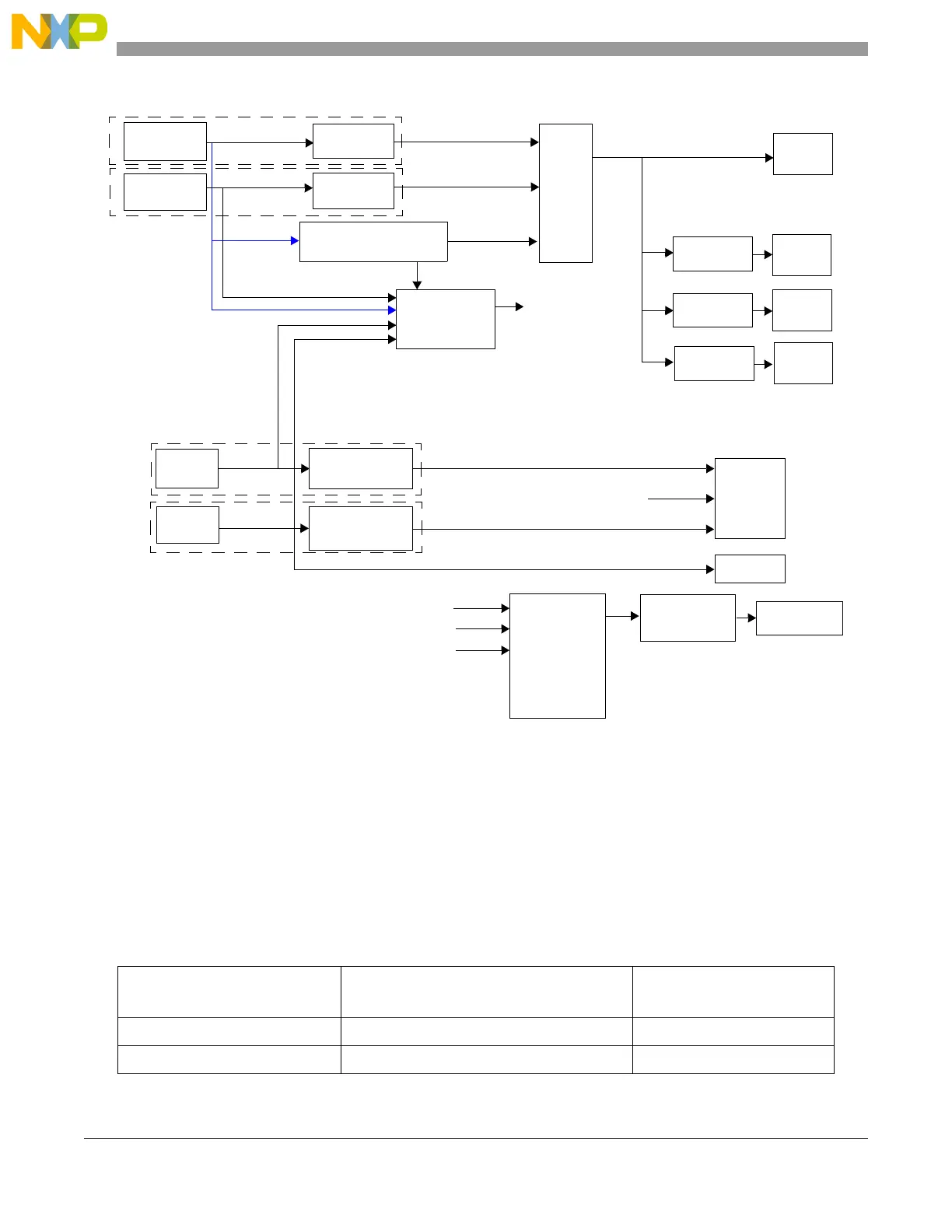

Figure 6-1. MPC5604B system clock generation

6.2 Clock gating

The MPC5604B provides the user with the possibility of gating the clock to the peripherals. Table 6-1

describes for each peripheral the associated gating register address. See the ME_PCTLn section in this

reference manual.

Additionally, peripheral set (1, 2 or 3) frequency can be configured to be an integer (1 to 16) divided

version of the main system clock. See the CGM_SC_DC0 section in this reference manual for details.

Table 6-1. MPC5604B — Peripheral clock sources

Peripheral

Register gating address offset

(base = 0xC3FDC0C0)

1

Peripheral set

2

RPP_Z0H Platform none (managed through ME mode) —

DSPI_n 4+n (n = 0..2) 2

FXOSC

FIRC

Clock Monitor

Unit

SIRC

Reset

System

Clock

Selector

FMPLL

FXOSC_div

FIRC_div

FMPLL

(e.g. 64 MHz)

SYSCLK

Core

Platform

Peripheral

Set 1

Peripheral

Set 2

SWT

API/RTC

SXOSC

SXOSC

(32 KHz)

/1 to /16

/1 to /16

SXOSC_div

SIRC_div

SIRC

SIRC

FIRC

FXOSC

CLKOUT (PA0)

/1, /2, /4, /8

FMPLL

FIRC

FXOSC

CLKOUT

Selector

Peripheral

Set 3

/1 to /16

/1 to /32

/1 to /32

FIRC_div

/1 to /32

/1 to /32

SIRC_clk_div

SXOSC_div

(128 kHz)

(4–16 MHz)

(16 MHz)

Safe

Interrupt

ME_<mode>_FIRCON

ME_<mode>_FXOSCON

FXOSC_CTL[OSCDIV]

FIRC_TRIM[FIRCDIV]

ME_<mode>

[SYSCLK]

ME_<mode>[FMPLLON] & FMPLL_CR

SXOSC_CTL

SIRC_CTL

SXOSC_CTL[OSCDIV]

SIRC_CTL[SIRCDIV]

CGM_OCDS_SC[SELCTL]

CGM_OCDS_SC[SELDIV]

CGM_SC_DC0

CGM_SC_DC1

CGM_SC_DC2

Loading...

Loading...