MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 495

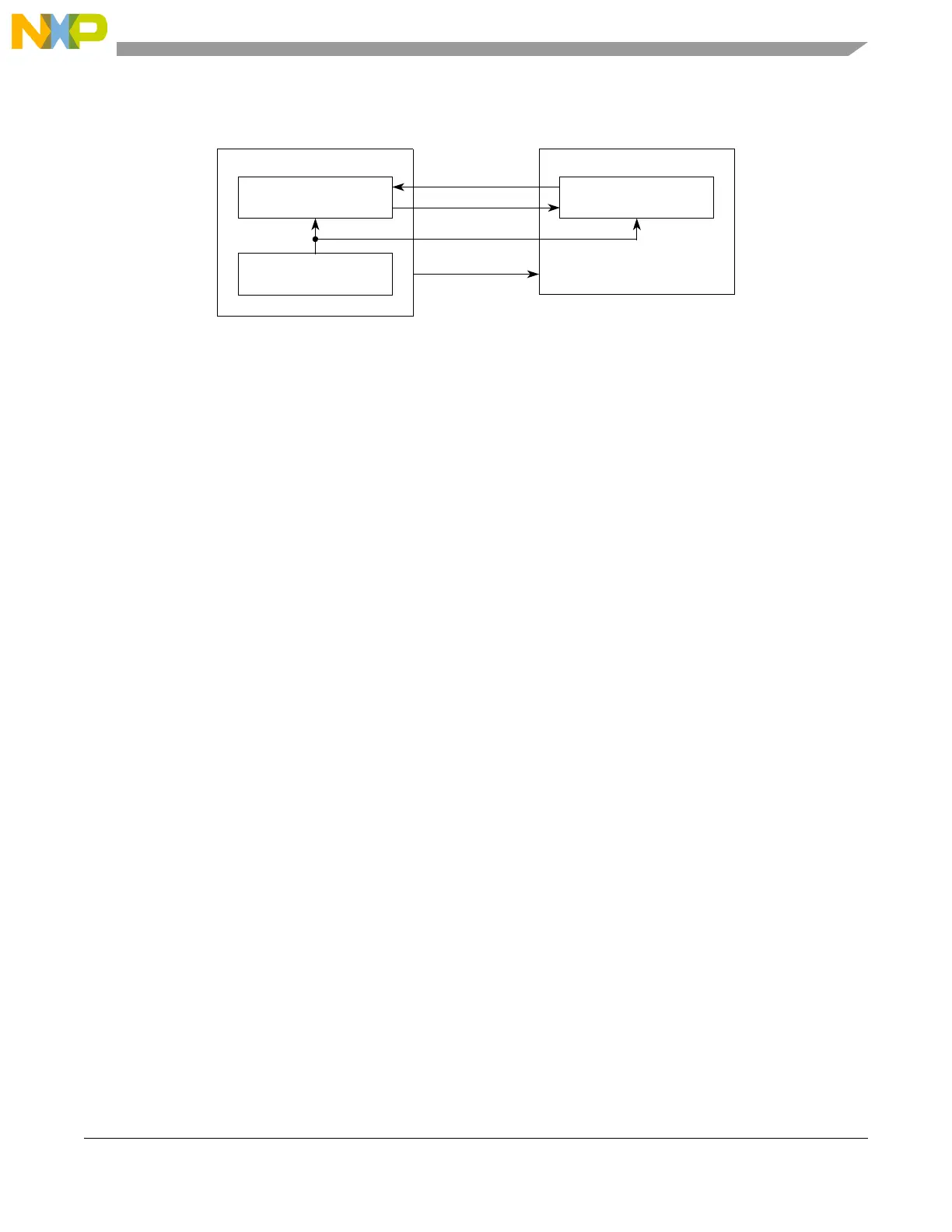

Figure 23-12. SPI serial protocol overview

The DSPI has six peripheral chip select (CSx) signals that are be used to select which of the slaves to

communicate with.

Transfer protocols and timing properties are shared by the three DSPI configurations; these properties are

described independently of the configuration in Section 23.6.5, Transfer formats. The transfer rate and

delay settings are described in Section 23.6.4, DSPI baud rate and clock delay generation.

See Section 23.6.8, Power saving features, for information on the power-saving features of the DSPI.

23.6.1 Modes of operation

The DSPI modules have the following available distinct modes:

• Master mode

• Slave mode

• Module Disable mode

• Debug mode

Master, slave, and module disable modes are module-specific modes whereas debug mode is

device-specific.

The module-specific modes are determined by bits in the DSPIx_MCR. Debug mode is a mode that the

entire device can enter in parallel with the DSPI being configured in one of its module-specific modes.

23.6.1.1 Master mode

In master mode the DSPI can initiate communications with peripheral devices. The DSPI operates as bus

master when the MSTR bit in the DSPIx_MCR is set. The serial communications clock (SCK) is

controlled by the master DSPI. All three DSPI configurations are valid in master mode.

In SPI configuration, master mode transfer attributes are controlled by the SPI command in the current TX

FIFO entry. The CTAS field in the SPI command selects which of the eight DSPIx_CTARs are used to set

the transfer attributes. Transfer attribute control is on a frame by frame basis.

See Section 23.6.3, Serial peripheral interface (SPI) configuration for more details.

DSPI Master

Shift register

Baud rate generator

DSPI Slave

Shift register

SOUT_x

SIN_x

SOUT_x SIN_x

SCK_x SCK_x

CS_x CS0_x

Loading...

Loading...