MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 737

28.4.2 Reset effects on SRAM accesses

Asynchronous reset will possibly corrupt SRAM if it asserts during a read or write operation to SRAM.

The completion of that access depends on the cycle at which the reset occurs. Data read from or written to

SRAM before the reset event occurred is retained, and no other address locations are accessed or changed.

In case of no access ongoing when reset occurs, the SRAM corruption does not happen.

Instead, synchronous reset (SW reset) should be used in controlled function (without SRAM accesses) in

case an initialization procedure without SRAM initialization is needed.

28.5 Functional description

ECC checks are performed during the read portion of an SRAM ECC read/write (R/W) operation, and

ECC calculations are performed during the write portion of a R/W operation. Because the ECC bits can

contain random data after the device is powered on, the SRAM must be initialized by executing 32-bit

write operations prior to any read accesses. This is also true for implicit read accesses caused by any write

accesses of less than 32 bits as discussed in Section 28.4, “SRAM ECC mechanism.

28.6 Initialization and application information

To use the SRAM, the ECC must check all bits that require initialization after power on. All writes must

specify an even number of registers performed on 32-bit word-aligned boundaries. If the write is not the

entire 32 bits (8 or 16 bits), a read / modify / write operation is generated that checks the ECC value upon

the read. See Section 28.4, “SRAM ECC mechanism.

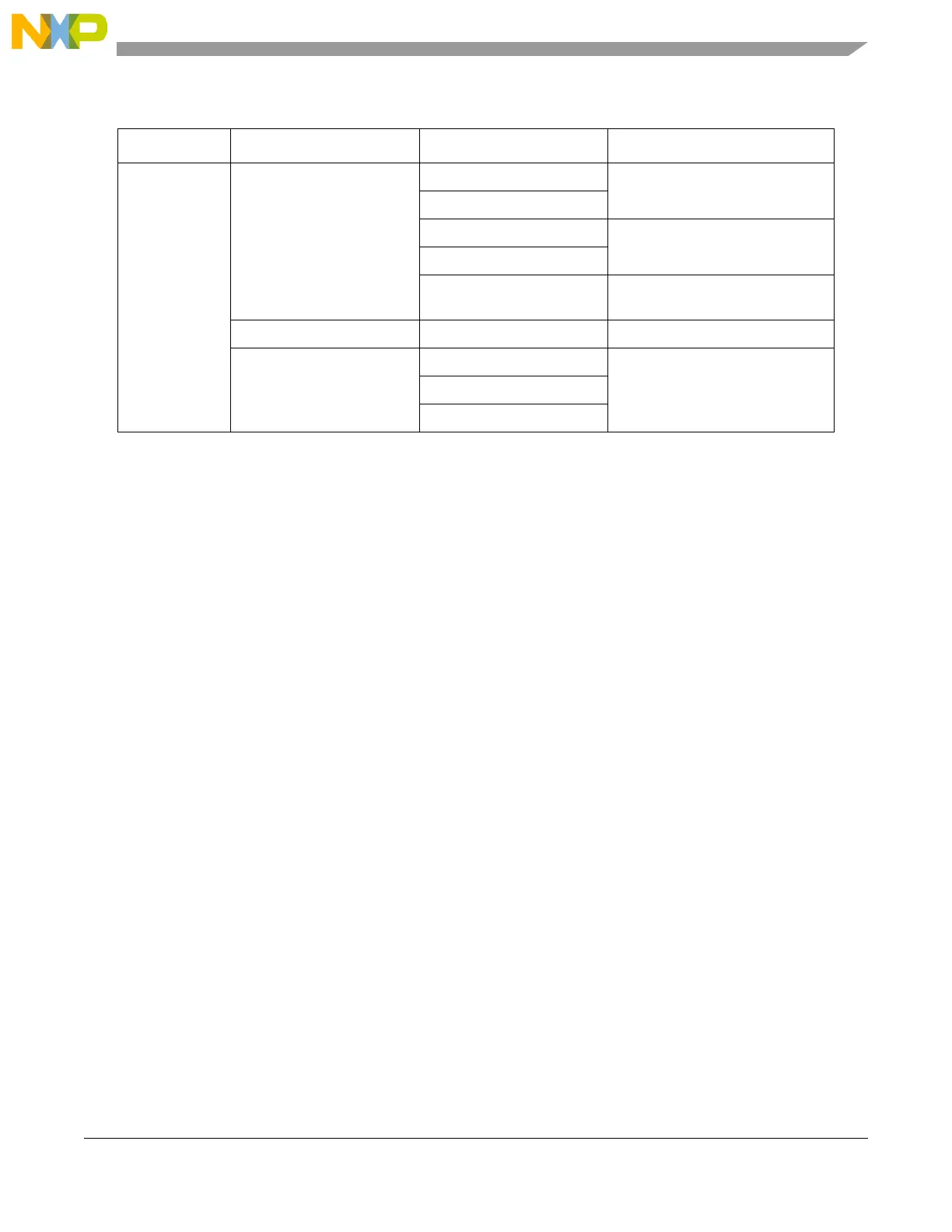

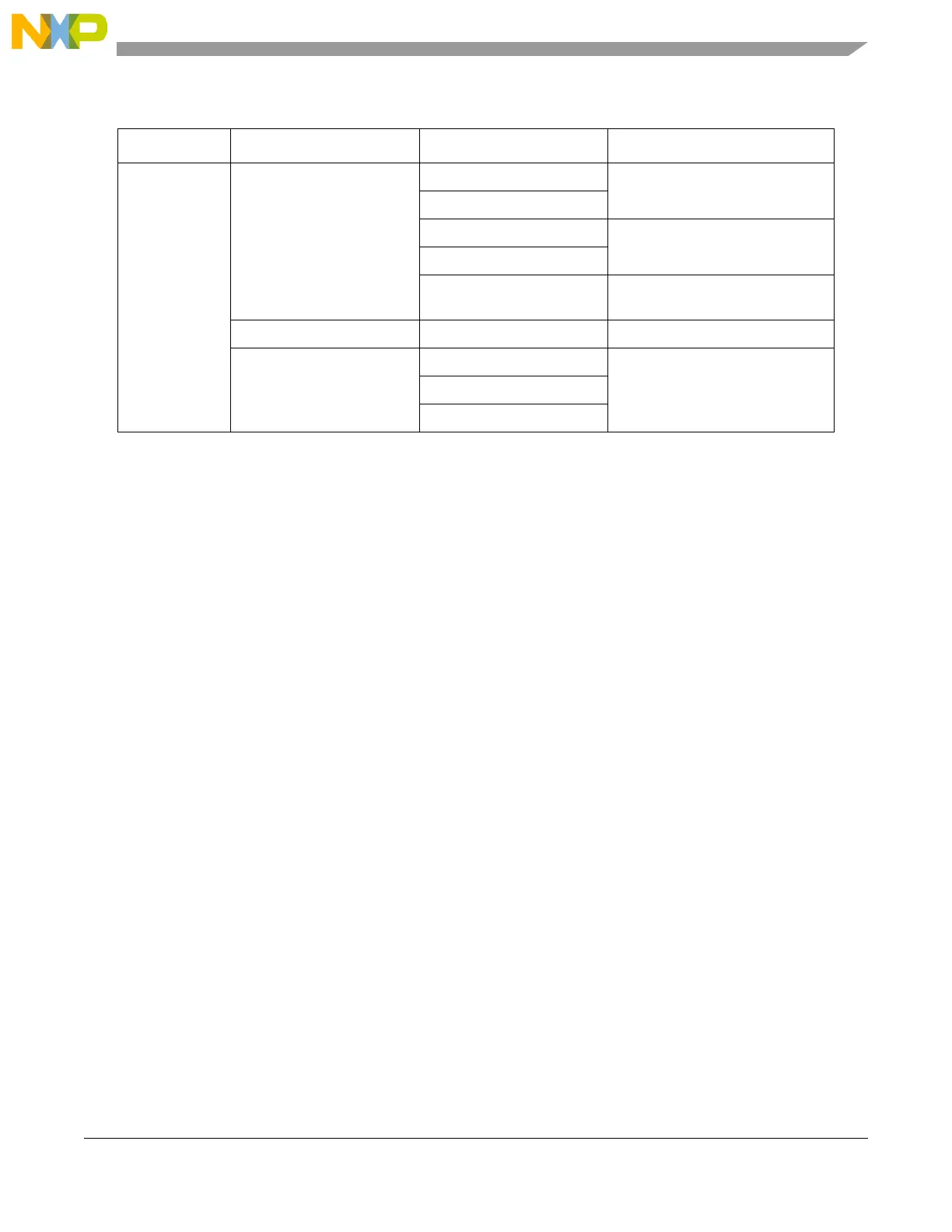

Write 8 or 16-bit write Idle 1

Read

Pipelined 8 or 16-bit write 2

32-bit write

8 or 16-bit write 0

(write to the same address)

Pipelined 8, 16 or 32-bit write 8, 16 or 32-bit write 0

32-bit write Idle 0

32-bit write

Read

Table 28-3. Number of wait states required for SRAM operations (continued)

Operation type Current operation Previous operation Number of wait states required

Loading...

Loading...