MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 331

19.5 Memory map and register description

This section provides a detailed description of all registers accessible in the SIUL module.

19.5.1 SIUL memory map

Table 19-2 gives an overview of the SIUL registers implemented.

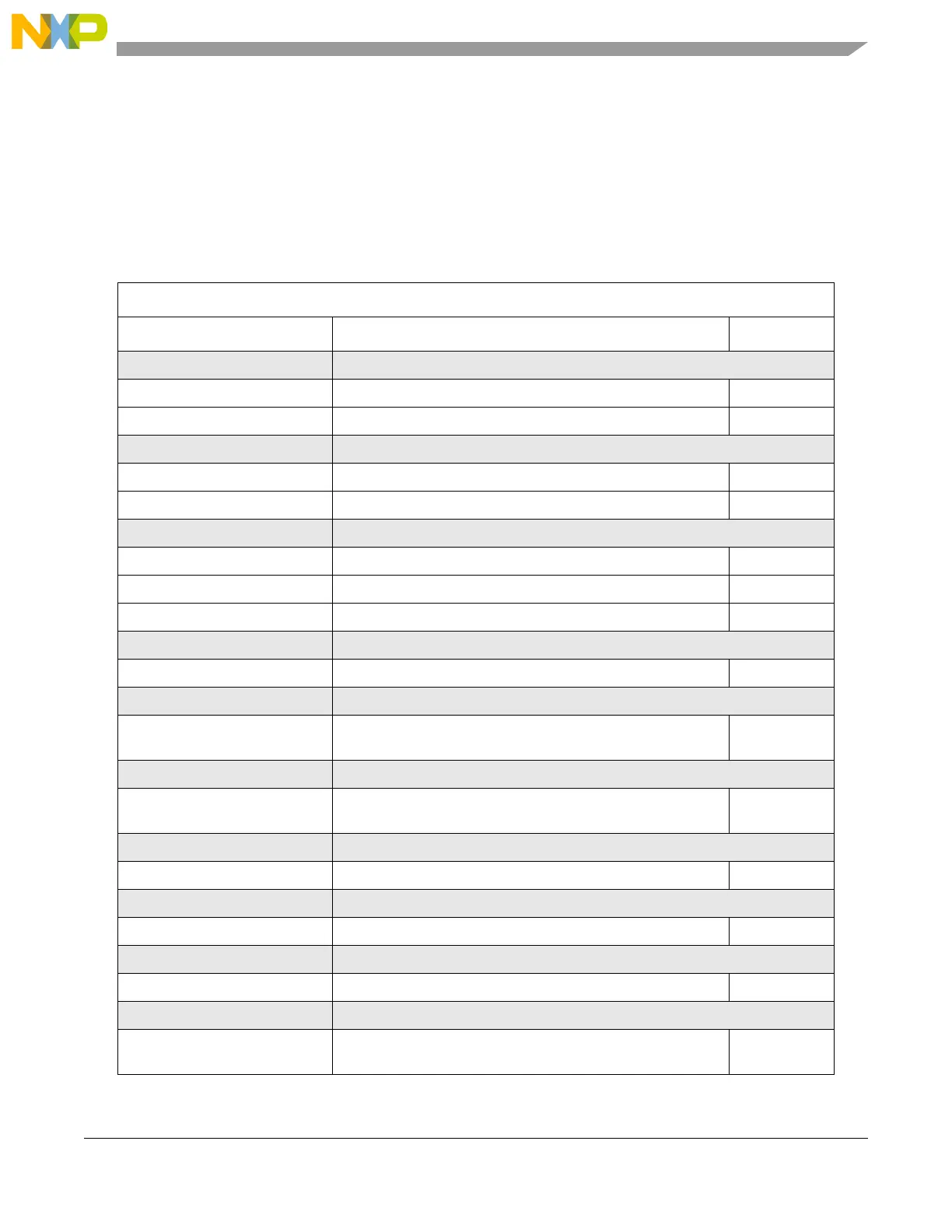

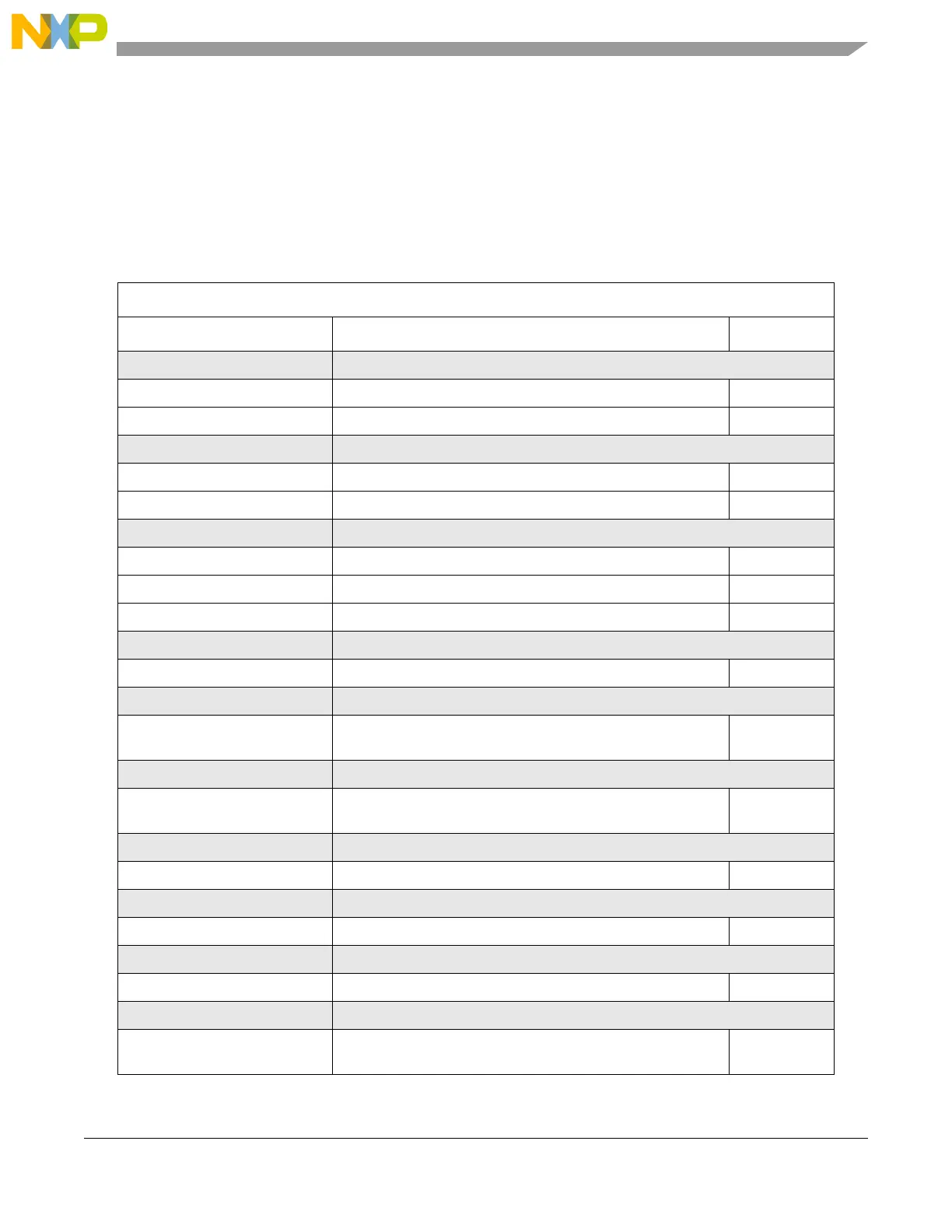

Table 19-2. SIUL memory map

Base address: 0xC3F9_0000

Address offset Register Location

0x0000 Reserved

0x0004 MCU ID Register #1 (MIDR1) on page 333

0x0008 MCU ID Register #2 (MIDR2) on page 334

0x000C–0x0013 Reserved

0x0014 Interrupt Status Flag Register (ISR) on page 335

0x0018 Interrupt Request Enable Register (IRER) on page 336

0x001C–0x0027 Reserved

0x0028 Interrupt Rising-Edge Event Enable Register (IREER) on page 336

0x002C Interrupt Falling-Edge Event Enable Register (IFEER) on page 337

0x0030 Interrupt Filter Enable Register (IFER) on page 338

0x0034–0x003F Reserved

0x0040–0x0134 Pad Configuration Registers (PCR0–PCR122)

1

on page 339

0x0136–0x04FF Reserved

0x0500–0x051C Pad Selection for Multiplexed Inputs Registers

(PSMI0_3–PSMI28_31)

on page 341

0x0520–0x05FF Reserved

0x0600–0x0678 GPIO Pad Data Output Registers

(GPDO0_3–GPDO120_123)

2,3

on page 344

0x067C–0x07FF Reserved

0x0800–0x0878 GPIO Pad Data Input Registers (GPDI0_3–GPDI120_123)

2,4

on page 345

0x087C–0x0BFF Reserved

0x0C00–0x0C0C Parallel GPIO Pad Data Out Registers (PGPDO0 – PGPDO3) on page 345

0x0C10–0x0C3F Reserved

0x0C40–0x0C4C Parallel GPIO Pad Data In Registers (PGPDI0 – PGPDI3) on page 346

0x0C50–0x0C7F Reserved

0x0C80–0x0C9C Masked Parallel GPIO Pad Data Out Register

(MPGPDO0–MPGPDO7)

on page 347

Loading...

Loading...