MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 343

19.5.3.10 GPIO Pad Data Output Registers (GPDO0_3–GPDO120_123)

These registers are used to set or clear GPIO pads. Each pad data out bit can be controlled separately with

a byte access.

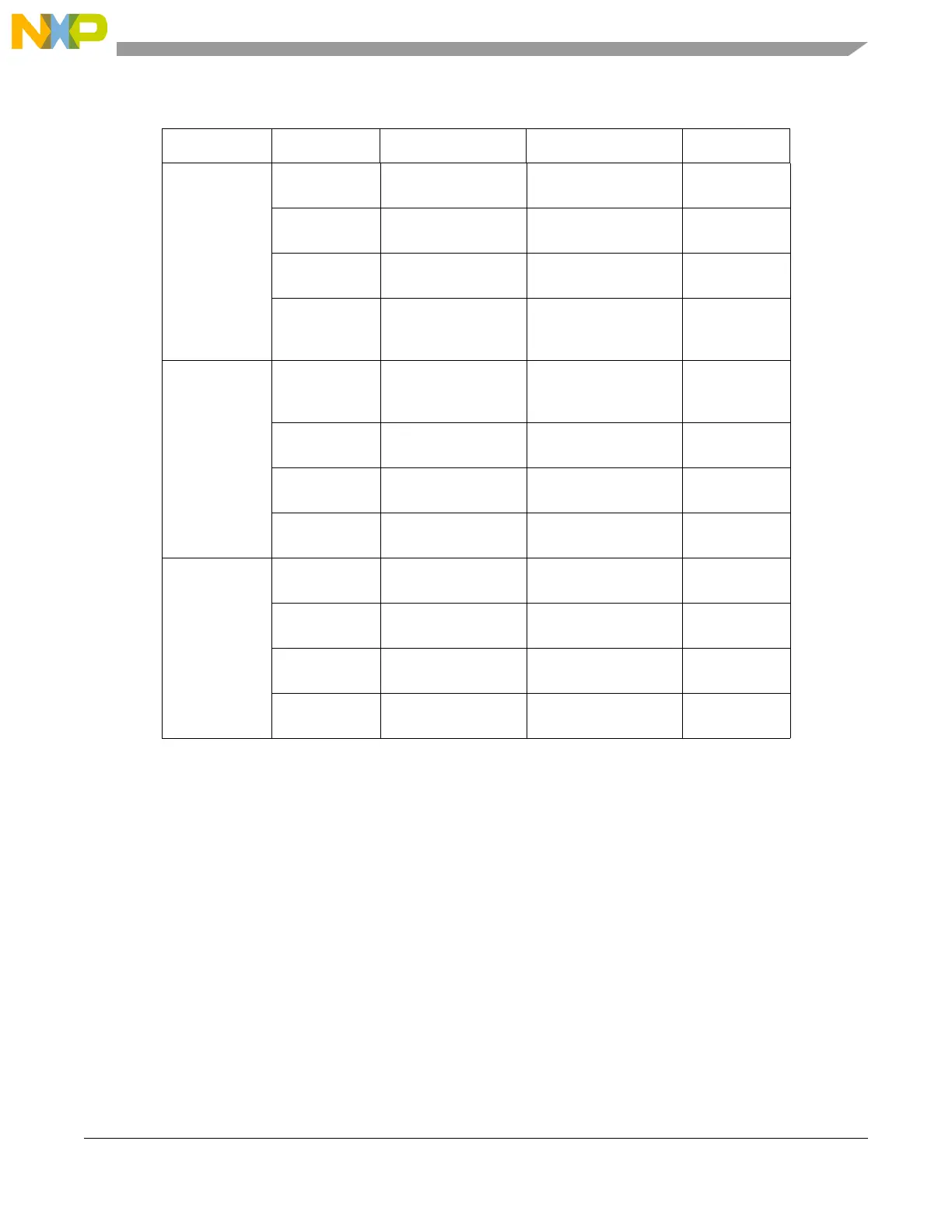

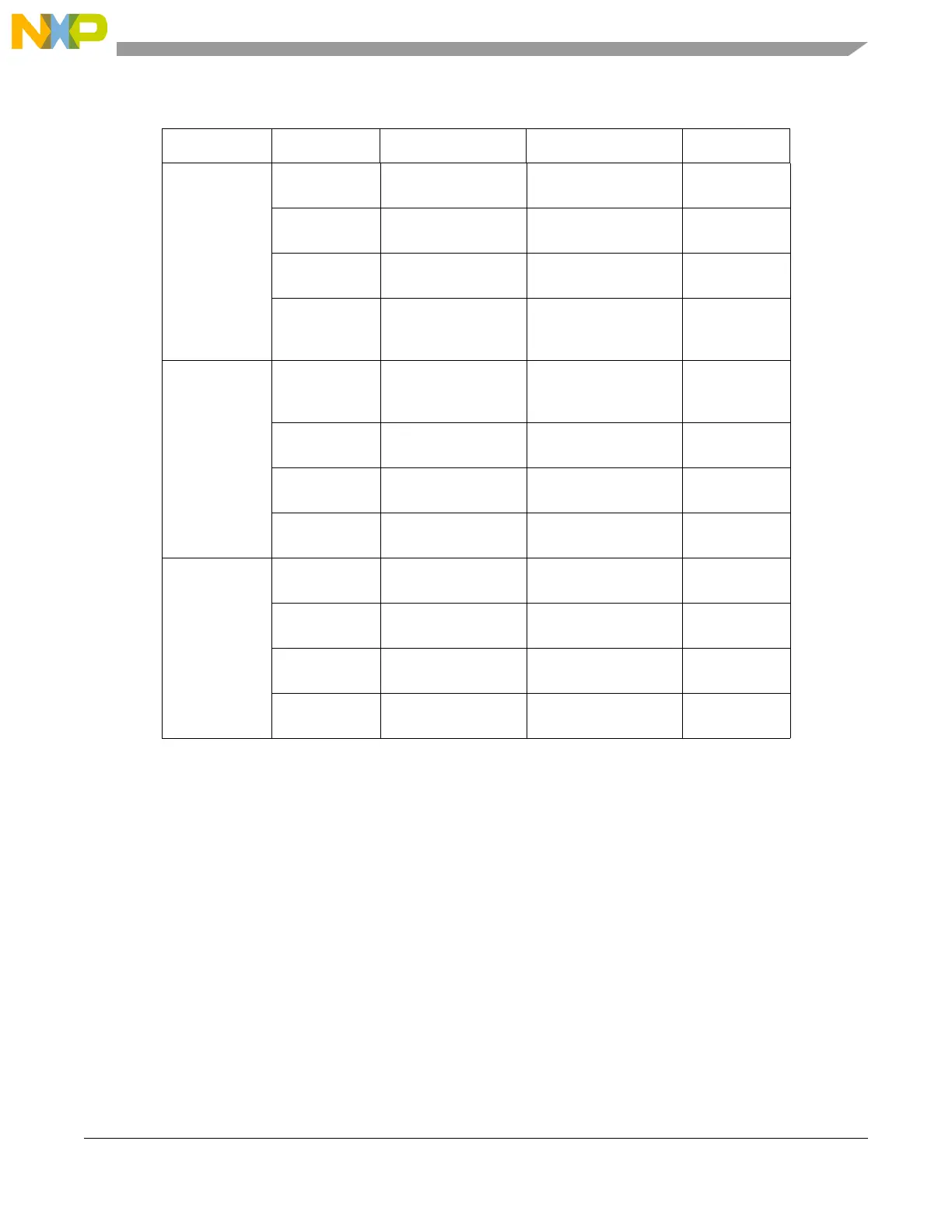

PSMI20_23 PADSEL20 0x514 E0UC[12] / eMIOS_0 00: PCR[44]

01: PCR[82]

2

PADSEL21 0x515 E0UC[13] / eMIOS_0 00: PCR[45]

01: PCR[83]

2

PADSEL22 0x516 E0UC[14] / eMIOS_0 00: PCR[46]

01: PCR[84]

2

PADSEL23 0x517 E0UC[22] / eMIOS_0 00: PCR[70]

01: PCR[72]

10: PCR[85]

2

PSMI24_27 PADSEL24 0x518 E0UC[23] / eMIOS_0 00: PCR[71]

01: PCR[73]

10: PCR[86]

2

PADSEL25

5

0x519 E0UC[24] / eMIOS_0 00: PCR[60]

01: PCR[106]

2

PADSEL26

5

0x51A E0UC[25] / eMIOS_0 00: PCR[61]

01: PCR[107]

2

PADSEL27

5

0x51B E0UC[26] / eMIOS_0 00: PCR[62]

01: PCR[108]

2

PSMI28_31 PADSEL28

5

0x51C E0UC[27] / eMIOS_0 00: PCR[63]

01: PCR[109]

2

PADSEL29 0x51D SCL / f_0 00: PCR[11]

01: PCR[19]

PADSEL30 0x51E SDA / I2C__0 00: PCR[10]

01: PCR[18]

PADSEL31 0x51F LIN3RX / LINFlex_3 00: PCR[8]

01: PCR[75]

1

See the signal description chapter of this reference manual for correspondence between PCR and

pinout

2

Not available in 100-pin LQFP

3

Not available on MPC5603B devices

4

Available only on MPC5604B 208 MAPBGA devices

5

Not available on MPC5602B and MPC5603B 100-pin devices

Table 19-13. Peripheral input pin selection (continued)

PSMI registers PADSEL fields SIUL address offset Function / Peripheral Mapping

1

Loading...

Loading...