MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 451

Registers apply to the 8 elements of the FIFO filter table (on a one-to-one correspondence), while the rest

of the registers apply to the regular MBs, starting from MB8.

The Individual Rx Mask Registers are implemented in SRAM, so they are not affected by reset and must

be explicitly initialized prior to any reception. Furthermore, they can only be accessed by the CPU while

the module is in Freeze Mode. Out of Freeze Mode, write accesses are blocked and read accesses will

return “all zeros”. Furthermore, if the BCC bit in the MCR is negated, any read or write operation to these

registers results in access error.

22.4 Functional description

22.4.1 Overview

The FlexCAN module is a CAN protocol engine with a very flexible mailbox system for transmitting and

receiving CAN frames. The mailbox system is composed by a set of up to 64 Message Buffers (MB) that

store configuration and control data, time stamp, message ID and data (see Section 22.3.2, “Message

buffer structure). The memory corresponding to the first 8 MBs can be configured to support a FIFO

reception scheme with a powerful ID filtering mechanism, capable of checking incoming frames against

a table of IDs (up to 8 extended IDs or 16 standard IDs or 32 8-bit ID slices), each one with its own

individual mask register. Simultaneous reception through FIFO and mailbox is supported. For mailbox

reception, a matching algorithm makes it possible to store received frames only into MBs that have the

same ID programmed on its ID field. A masking scheme makes it possible to match the ID programmed

on the MB with a range of IDs on received CAN frames. For transmission, an arbitration algorithm decides

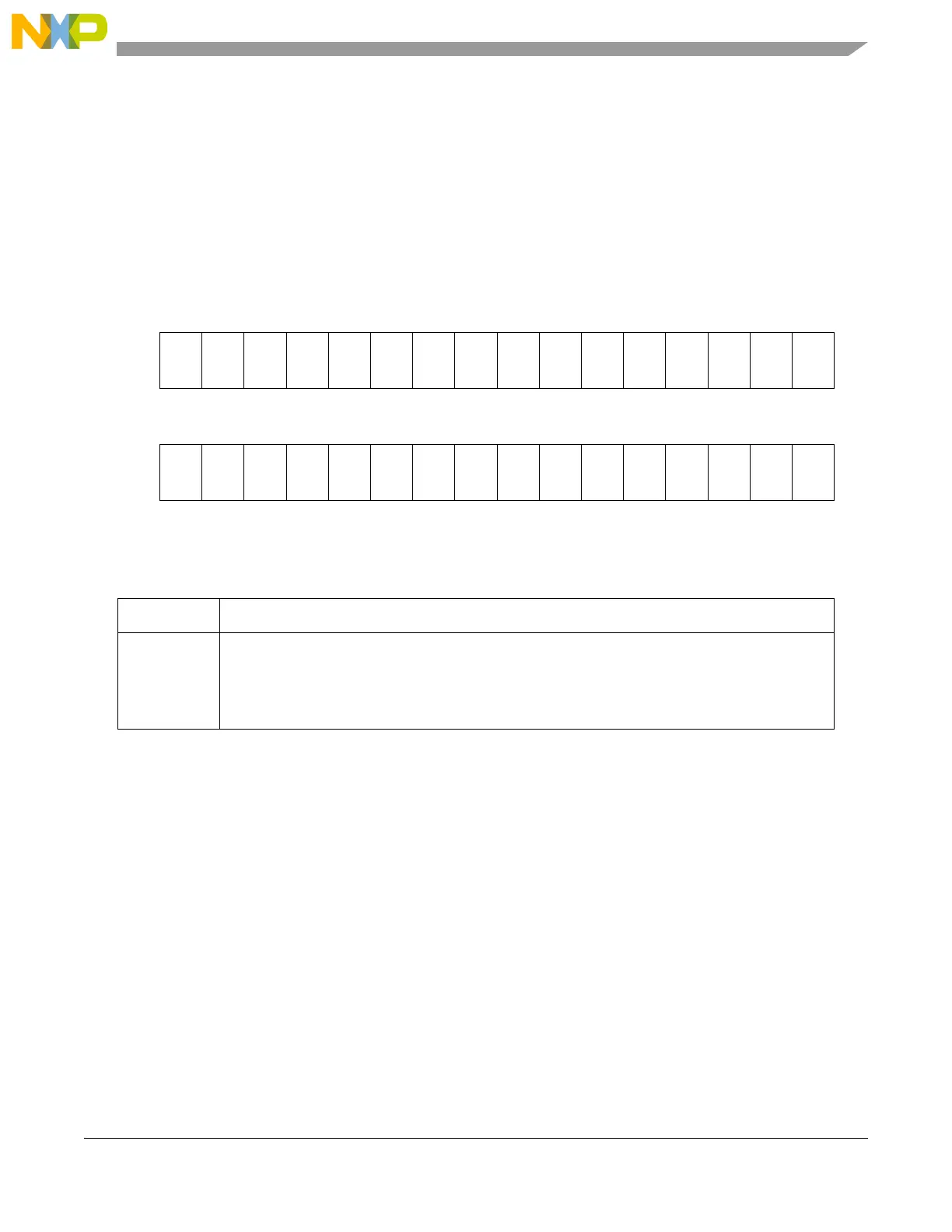

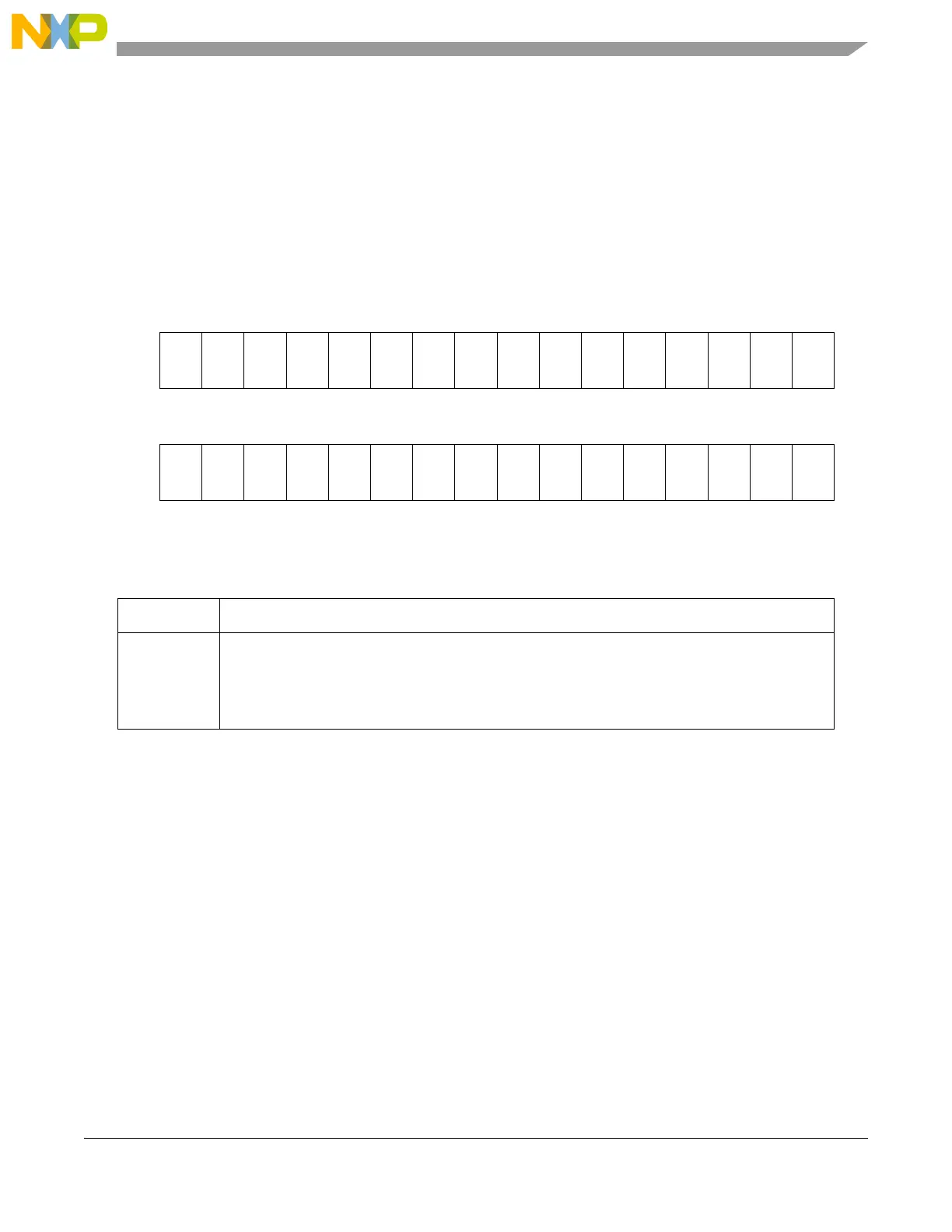

Base + 0x0004

0123456789101112131415

MI31 MI30 MI29 MI28 MI27 MI26 MI25 MI24 MI23 MI22 MI21 MI20 MI19 MI18 MI17 MI16

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

MI15 MI14 MI13 MI12 MI11 MI10 MI9 MI8 MI7 MI6 MI5 MI4 MI3 MI2 MI1 MI0

Figure 22-15. Rx Individual Mask Registers (RXIMR0 – RXIMR63)

Table 22-18. RXIMR0 – RXIMR63 field description

Field Description

MI31–MI0 Mask Bits

For normal Rx MBs, the mask bits affect the ID filter programmed on the MB. For the Rx FIFO, the

mask bits affect all bits programmed in the filter table (ID, IDE, RTR).

1 = The corresponding bit in the filter is checked against the one received

0 = the corresponding bit in the filter is “don’t care”

Loading...

Loading...