MPC5604B/C Microcontroller Reference Manual, Rev. 8

680 Freescale Semiconductor

27.5.2 DFlash register description

27.5.2.1 DFlash Module Configuration Register (DFLASH_MCR)

The Module Configuration Register is used to enable and monitor all modify operations of the flash

memory module.

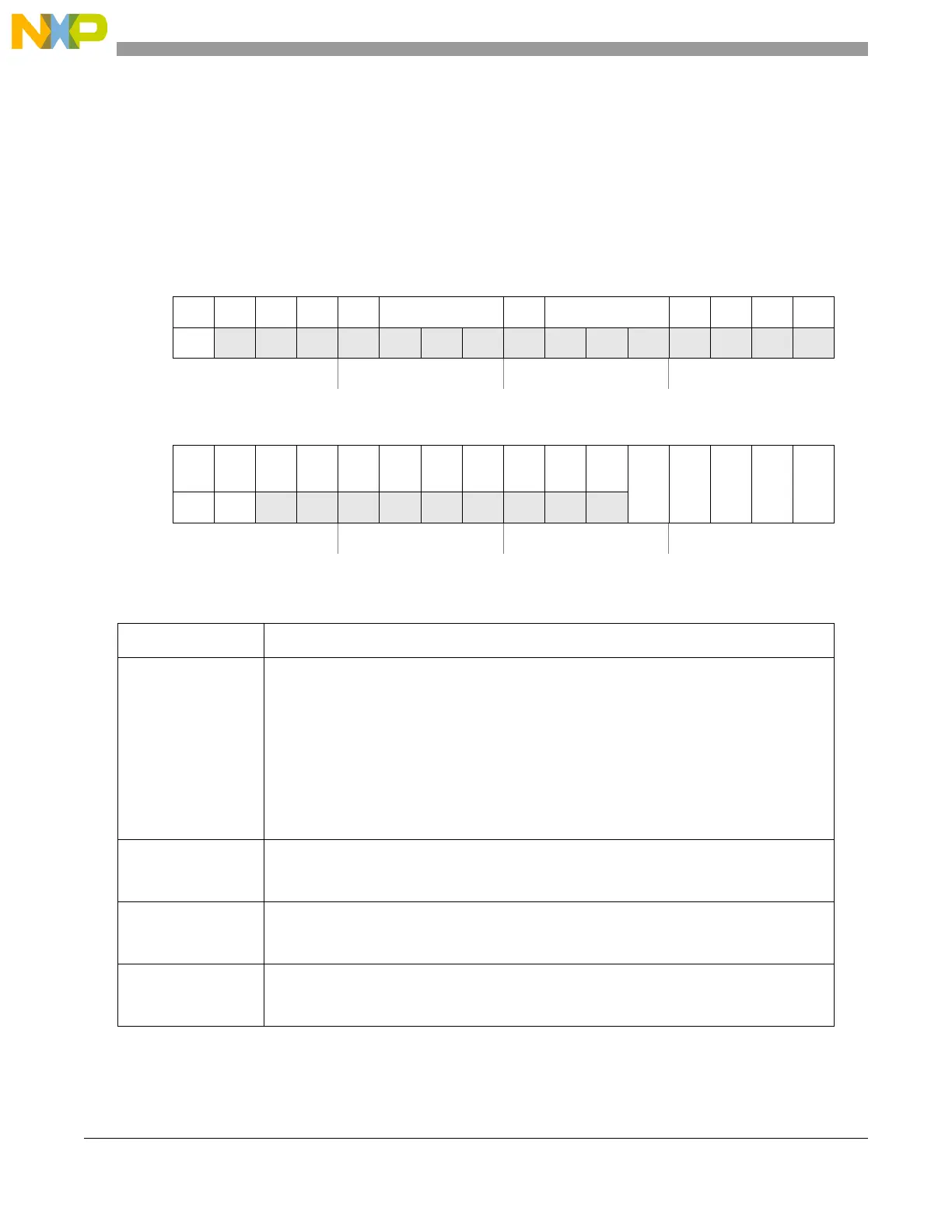

Address offset: 0x0000 Access: Read/write

0123456789101112131415

R

EDC0000 SIZE 0 LAS 000MAS

W

w1c

Reset

0000011001100000

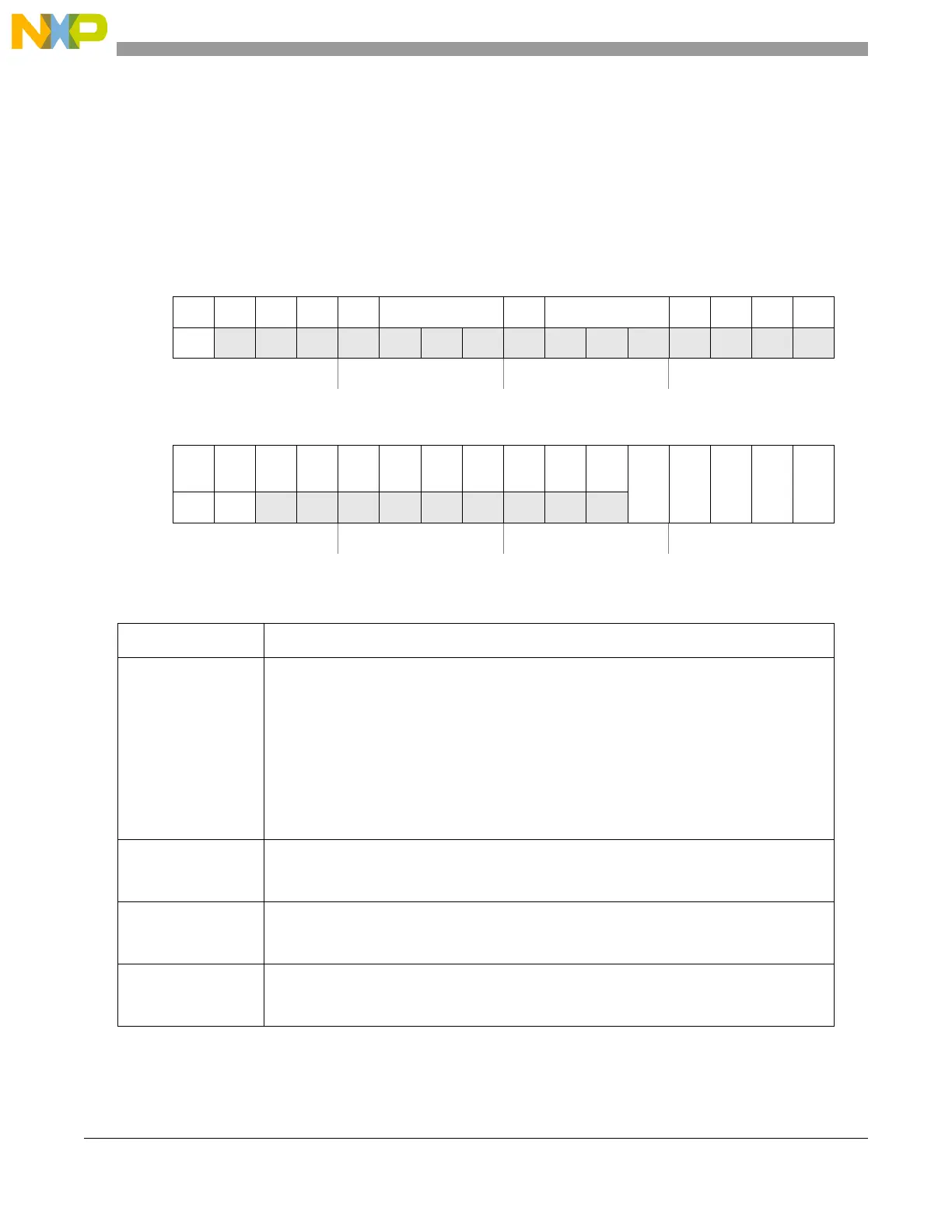

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

EER RWE 0 0

PEAS

DONE

PEG0000

PGM

PSUS

ERS

ESUS

EHV

W

w1c w1c

Reset

0000011000000000

Figure 27-23. DFlash Module Configuration Register (DFLASH_MCR)

Table 27-34. DFLASH_MCR field descriptions

Field Description

EDC ECC Data Correction

EDC provides information on previous reads. If an ECC Single Error detection and correction

occurred, the EDC bit is set to ‘1’. This bit must then be cleared, or a reset must occur before

this bit will return to a 0 state. This bit may not be set to ‘1’ by the user.

In the event of an ECC Double Error detection, this bit will not be set.

If EDC is not set, or remains 0, this indicates that all previous reads (from the last reset, or

clearing of EDC) were not corrected through ECC.

The function of this bit is device dependent and it can be configured to be disabled.

0: Reads are occurring normally.

1: An ECC Single Error occurred and was corrected during a previous read.

SIZE array space SIZE

The value of SIZE field is dependent upon the size of the flash memory module; see

Table 27-35.

LAS Low Address Space

The value of the LAS field corresponds to the configuration of the Low Address Space; see

Table 27-36.

MAS Mid Address Space

The value of the MAS field corresponds to the configuration of the Mid Address Space; see

Table 27-37.

Loading...

Loading...