MPC5604B/C Microcontroller Reference Manual, Rev. 8

470 Freescale Semiconductor

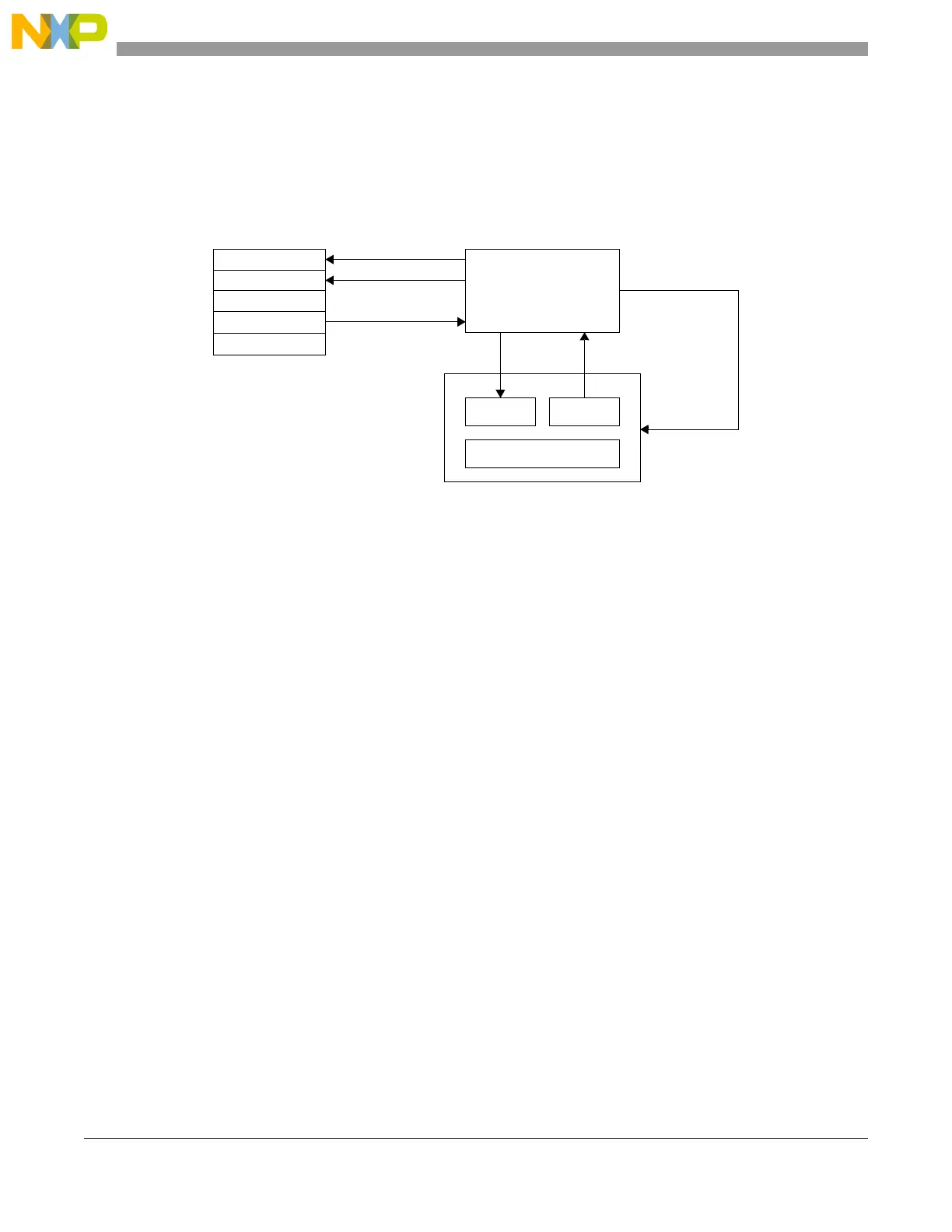

For queued operations the SPI queues reside in internal SRAM which is external to the DSPI. Data

transfers between the queues and the DSPI FIFOs are accomplished through host software.

Figure 23-2 shows a DSPI with external queues in internal SRAM.

Figure 23-2. DSPI with queues

23.2 Features

The DSPI supports these SPI features:

• Full-duplex, three-wire synchronous transfers

• Master and slave mode

• Buffered transmit and receive operation using the TX and RX FIFOs, with depths of four entries

• Visibility into TX and RX FIFOs for ease of debugging

• FIFO bypass mode for low-latency updates to SPI queues

• Programmable transfer attributes on a per-frame basis

— 6 clock and transfer attribute registers

— Serial clock with programmable polarity and phase

— Programmable delays

– CS to SCK delay

– SCK to CS delay

– Delay between frames

— Programmable serial frame size of 4 to 16 bits, expandable with software control

— Continuously held chip select capability

• Up to 6 peripheral chip selects, expandable to 64 with external demultiplexer

• Deglitching support for up to 32 peripheral chip selects with external demultiplexer

• 6 interrupt conditions:

Internal SRAM

TX queue

RX queue

Address/control

TX FIFO

DSPI

RX FIFO

RX data

TX data

TX data RX data

Shift register

Address/control

Host CPU

Loading...

Loading...