MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 823

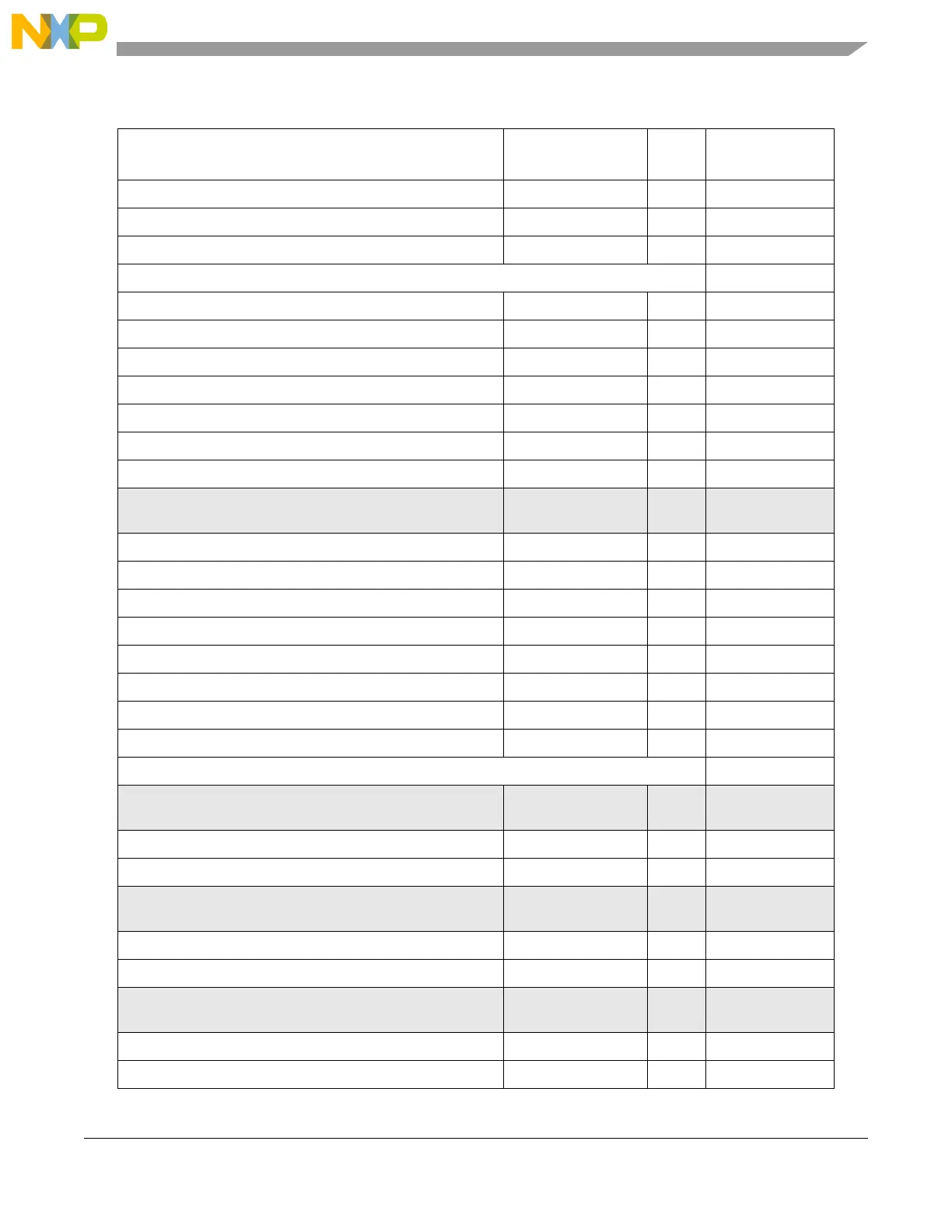

User Multiple Input Signature Register 2 CFLASH_UMISR2 32-bit Base + 0x0050

User Multiple Input Signature Register 3 CFLASH_UMISR3 32-bit Base + 0x0054

User Multiple Input Signature Register 4 CFLASH_UMISR4 32-bit Base + 0x0058

Data Flash A Configuration 0xC3F8_C000

Module Configuration Register DFLASH_MCR 32-bit Base + 0x0000

Low/Mid Address Space Block Locking Register DFLASH_LML 32-bit Base + 0x0004

High Address Space Block Locking Register DFLASH_HBL 32-bit Base + 0x0008

Secondary Low/Mid Address Space Block Locking Register DFLASH_SLL 32-bit Base + 0x000C

Low/Mid Address Space Block Select Register DFLASH_LMS 32-bit Base + 0x0010

High Address Space Block Select Register DFLASH_HBS 32-bit Base + 0x0014

Address Register DFLASH_ADR 32-bit Base + 0x0018

Reserved — — (Base + 0x001C) –

(Base + 0x003B)

User Test Register 0 DFLASH_UT0 32-bit Base + 0x003C

User Test Register 1 DFLASH_UT1 32-bit Base + 0x0040

User Test Register 2 DFLASH_UT2 32-bit Base + 0x0044

User Multiple Input Signature Register 0 DFLASH_UMISR0 32-bit Base + 0x0048

User Multiple Input Signature Register 1 DFLASH_UMISR1 32-bit Base + 0x004C

User Multiple Input Signature Register 2 DFLASH_UMISR2 32-bit Base + 0x0050

User Multiple Input Signature Register 3 DFLASH_UMISR3 32-bit Base + 0x0054

User Multiple Input Signature Register 4 DFLASH_UMISR4 32-bit Base + 0x0058

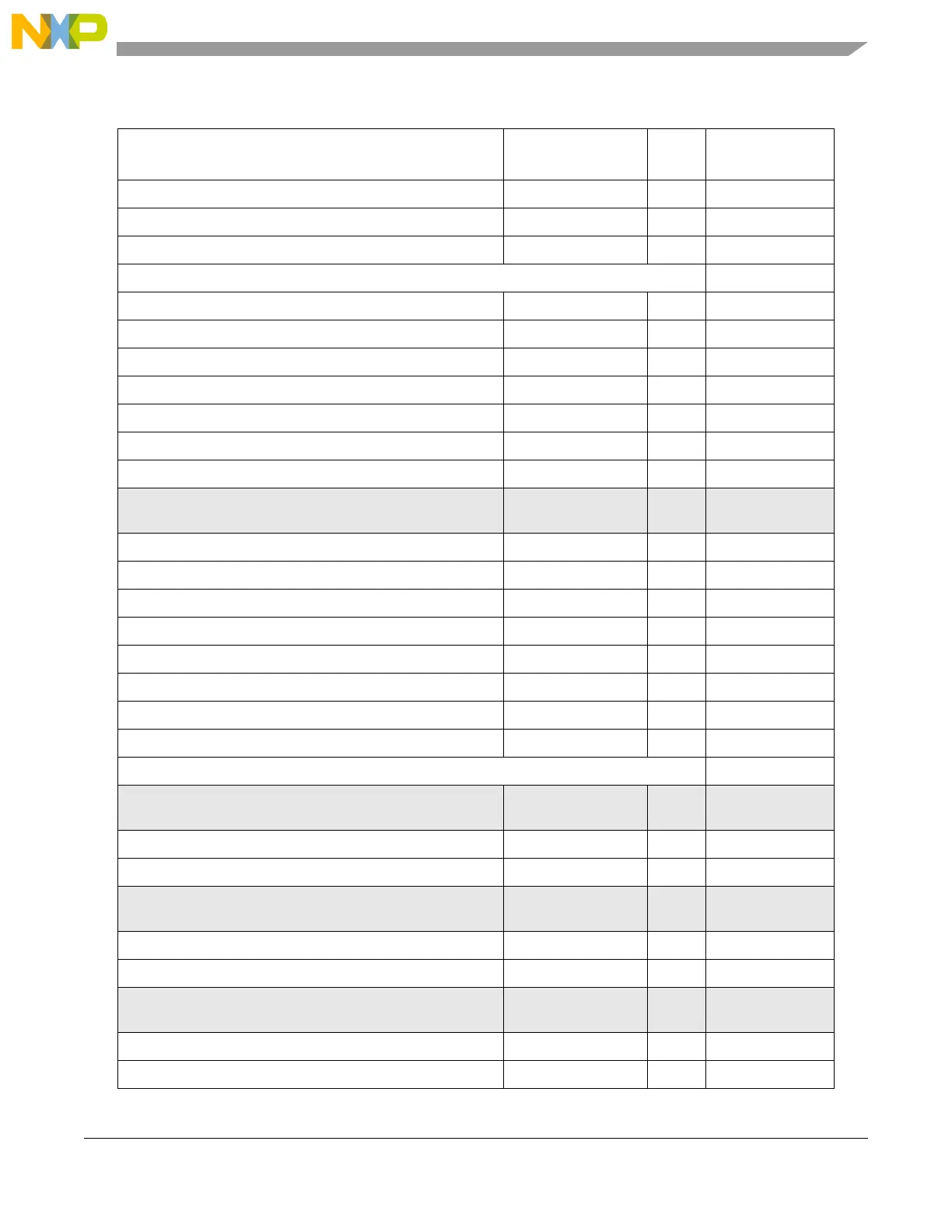

System Integration Unit Lite (SIUL) 0xC3F9_0000

Reserved — — Base + (0x0000 –

0x0003)

MCU ID Register 1 MIDR1 32-bit Base + 0x0004

MCU ID Register 2 MIDR2 32-bit Base + 0x0008

Reserved — — Base + (0x000C –

0x0013)

Interrupt Status Flag Register ISR 32-bit Base + 0x0014

Interrupt Request Enable Register IRER 32-bit Base + 0x0018

Reserved — — Base + (0x001C –

0x0027)

Interrupt Rising Edge Event Enable IREER 32-bit Base + 0x0028

Interrupt Falling-Edge Event Enable IFEER 32-bit Base + 0x002C

Table A-2. Detailed register map (continued)

Register description Register name

Used

size

Address

Loading...

Loading...