MPC5604B/C Microcontroller Reference Manual, Rev. 8

102 Freescale Semiconductor

6.6.3 Register description

6.7 Frequency-modulated phase-locked loop (FMPLL)

6.7.1 Introduction

This section describes the features and functions of the FMPLL module implemented in the device.

6.7.2 Overview

The FMPLL enables the generation of high speed system clocks from a common 4–16 MHz input clock.

Further, the FMPLL supports programmable frequency modulation of the system clock. The FMPLL

multiplication factor and output clock divider ratio are all software configurable.

MPC5604B has one FMPLL that can generate the system clock and takes advantage of the FM mode.

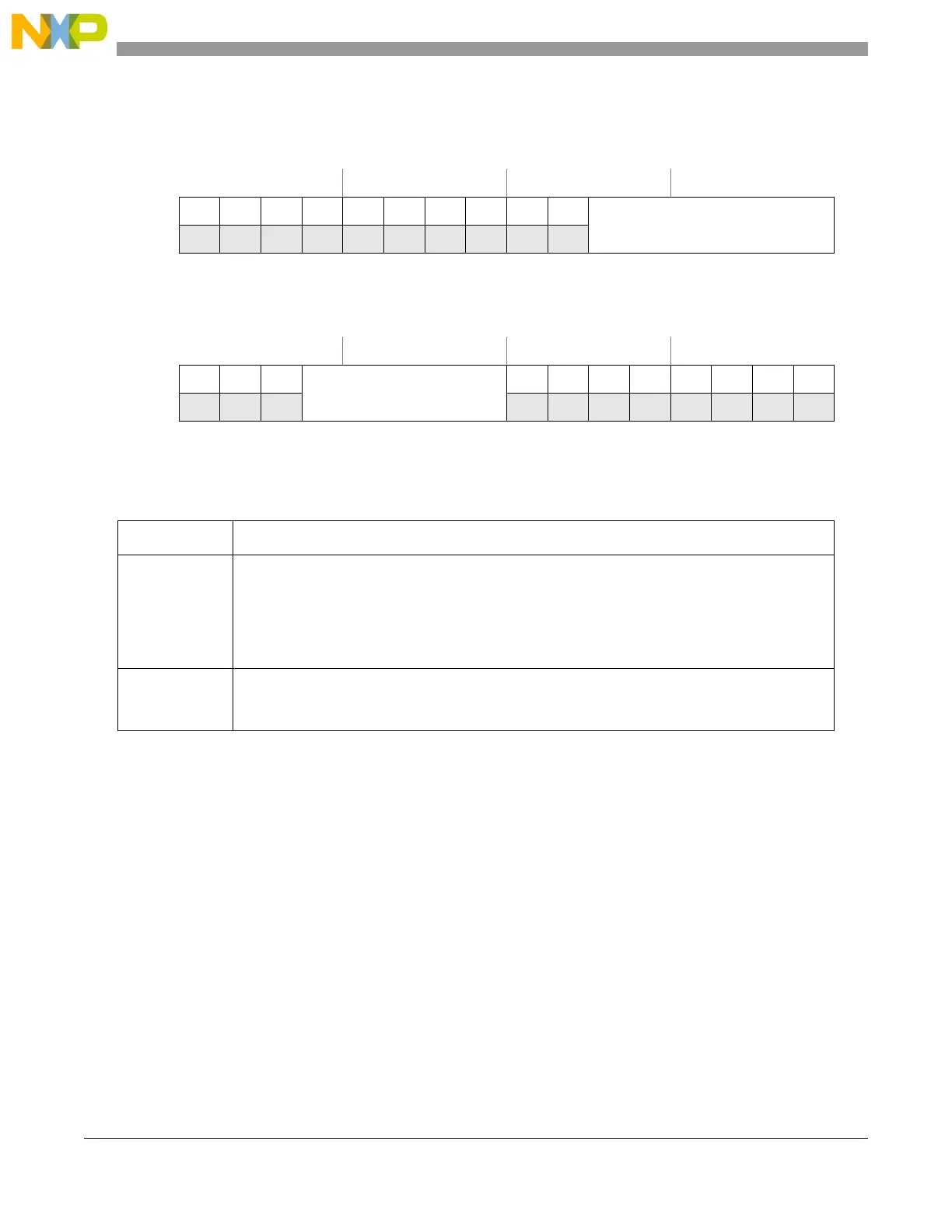

Address: 0xC3FE_0060 Access: Read/write

0123456789101112131415

R0000000000

FIRCTRIM

W

RESET:

0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0 0 0

FIRCDIV

00000000

W

RESET:

0000000000000000

Figure 6-5. FIRC Oscillator Control Register (FIRC_CTL)

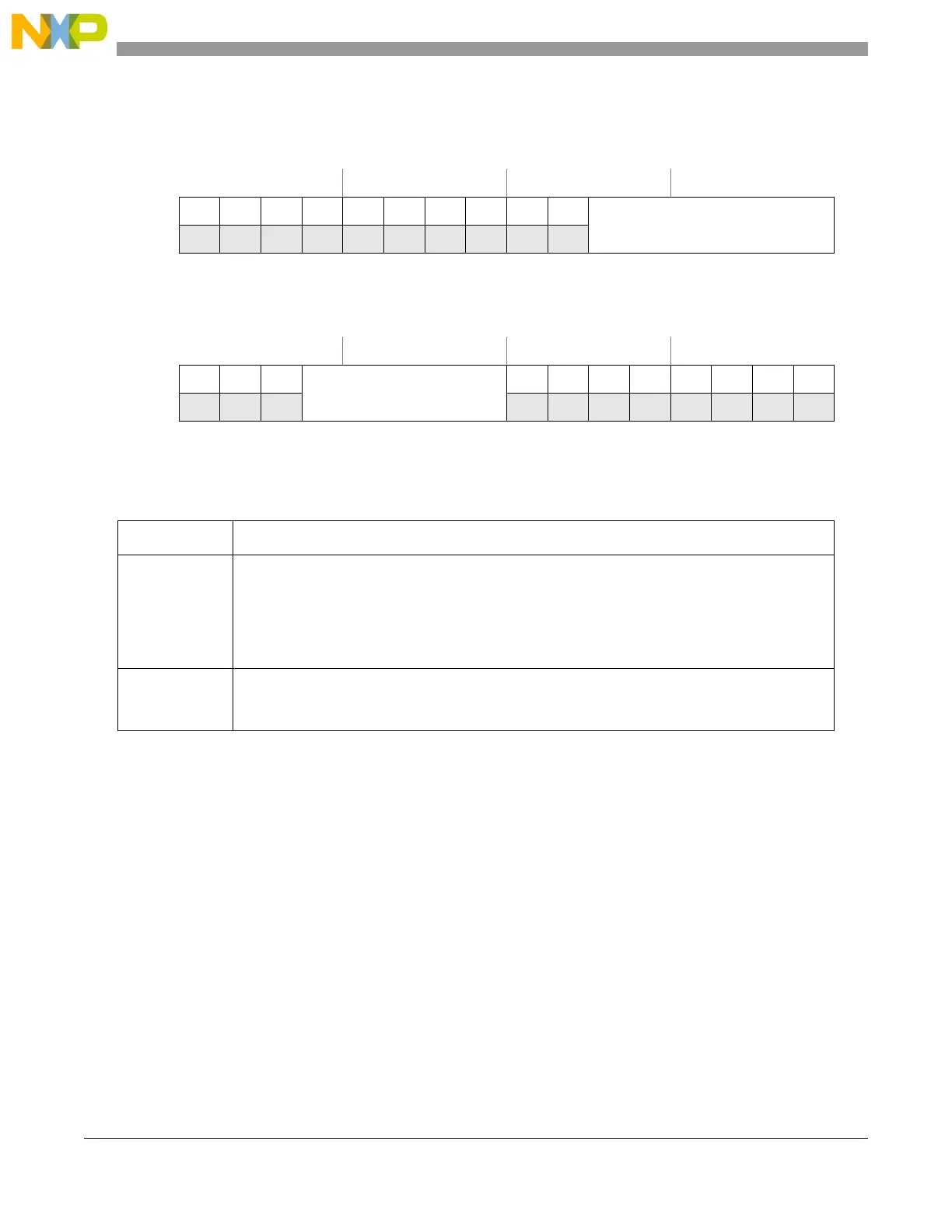

Table 6-7. FIRC_CTL field descriptions

Field Description

FIRCTRIM FIRC trimming bits.

This field corresponds (via two’s complement) to a trim factor of –16 to +15.

A +1 change in FIRCTRIM decreases the current frequency by

FIRCTRIM

(see the device data

sheet).

A –1 change in SIRCTRIM increases the current frequency by

FIRCTRIM

(see the device data

sheet).

FIRCDIV FIRC clock division factor.

This field specifies the FIRC oscillator output clock division factor. The output clock is divided by

the factor FIRCDIV+1.

Loading...

Loading...