MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 83

5.3.3 Modes of operation

The SSCM operates identically in all system modes.

5.3.4 Memory map and register description

Table 5-10 shows the memory map for the SSCM. Note that all addresses are offsets; the absolute address

may be calculated by adding the specified offset to the base address of the SSCM.

All registers are accessible via 8-bit, 16-bit or 32-bit accesses. However, 16-bit accesses must be aligned

to 16-bit boundaries, and 32-bit accesses must be aligned to 32-bit boundaries. As an example, the

SSCM_STATUS register is accessible by a 16-bit read/write to address ‘Base + 0x0002’, but performing

a 16-bit access to ‘Base + 0x0003’ is illegal.

5.3.4.1 System Status Register (SSCM_STATUS)

The System Status register is a read-only register that reflects the current state of the system.

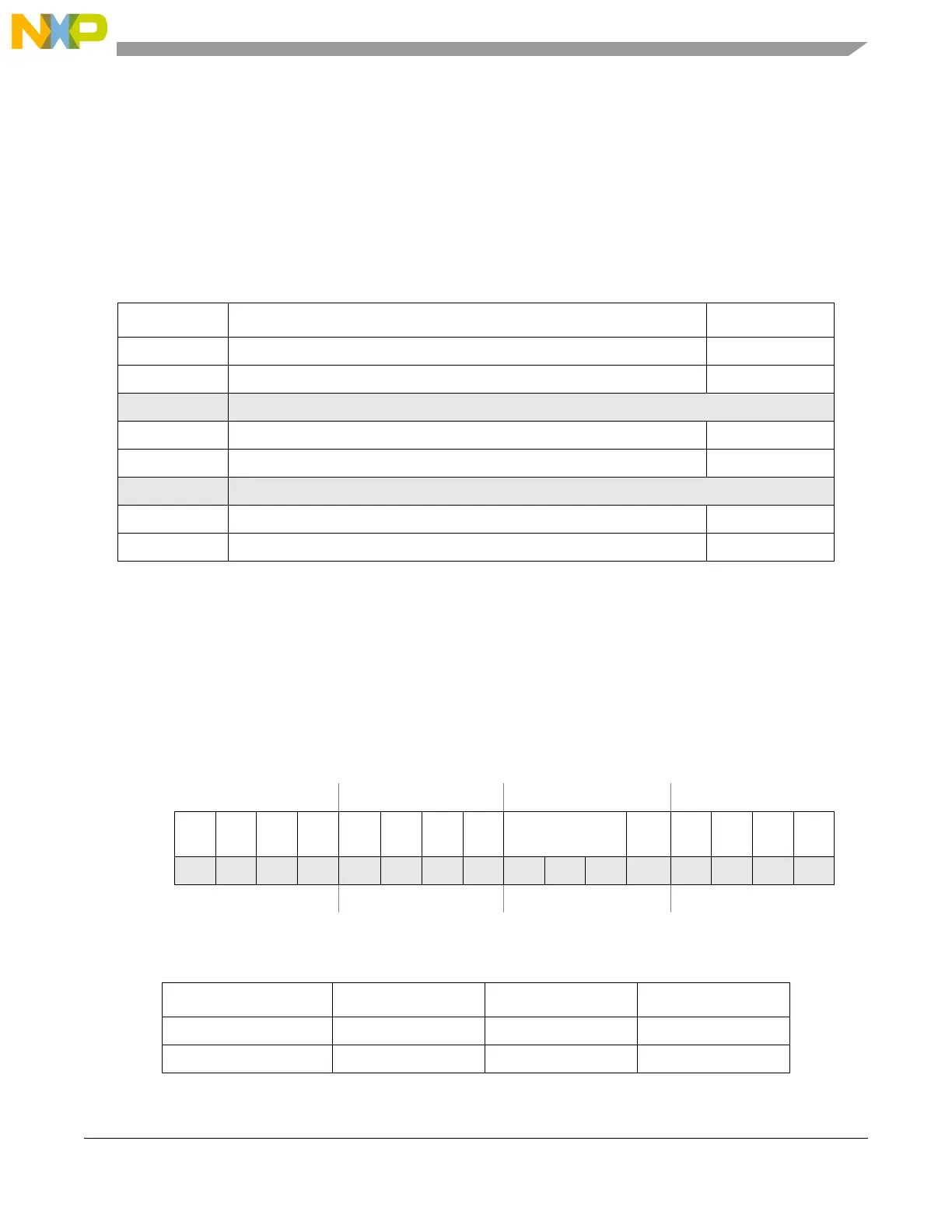

Table 5-10. SSCM memory map

Address offset Register Location

0x00 System Status Register (SSCM_STATUS) on page 83

0x02 System Memory Configuration Register (SSCM_MEMCONFIG) on page 84

0x04 Reserved

0x06 Error Configuration (SSCM_ERROR) on page 85

0x08 Debug Status Port Register (SSCM_DEBUGPORT) on page 86

0x0A Reserved

0x0C Password Comparison Register High Word (SSCM_PWCMPH) on page 87

0x10 Password Comparison Register Low Word (SSCM_PWCMPL) on page 87

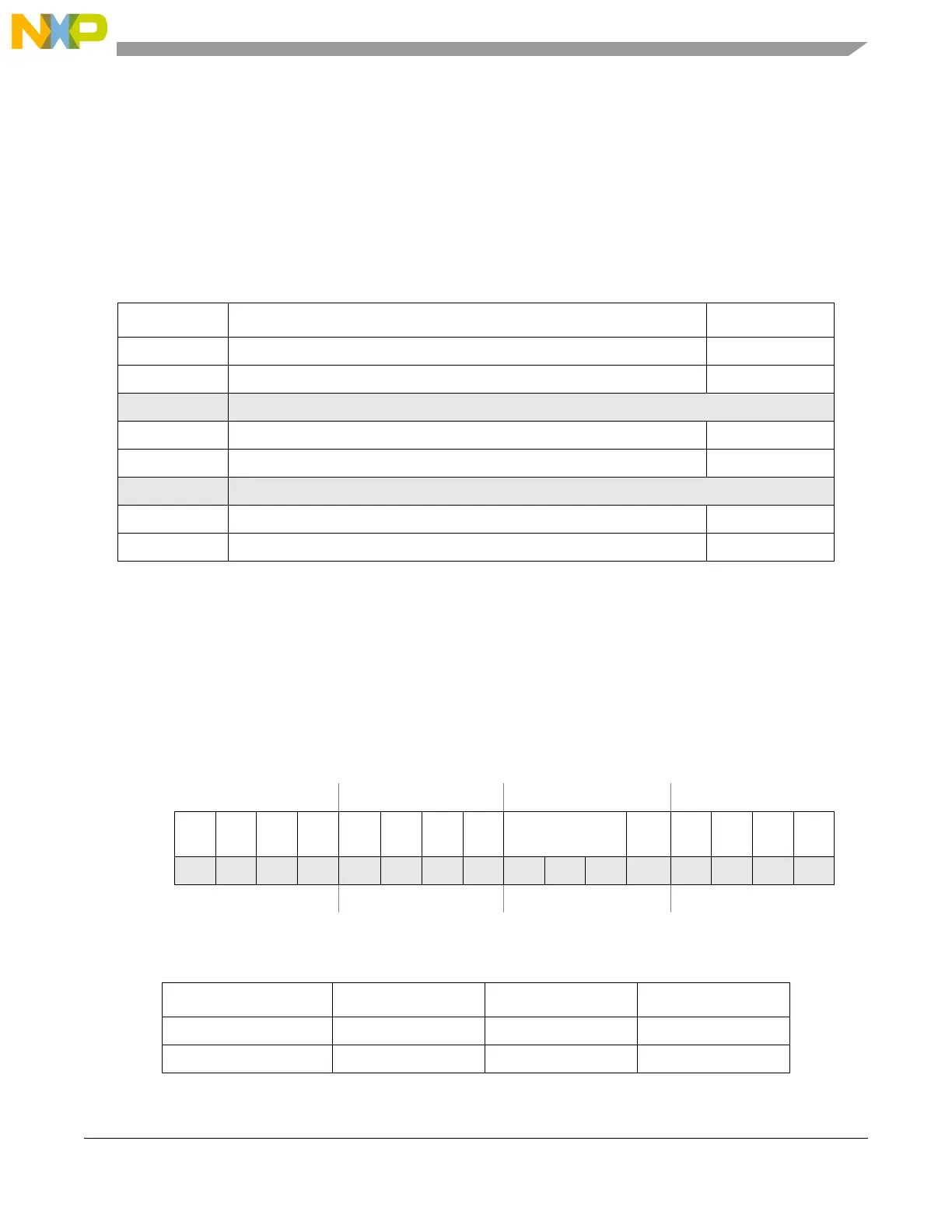

Offset:0x00 Access: Read

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

0000

NXEN

PUB SEC 0 BMODE 0 0 0 0 0

W

Reset000000000/10/10/10 0000

Figure 5-13. System Status Register (SSCM_STATUS)

Table 5-11. SSCM_STATUS allowed register accesses

Access type 8-bit 16-bit 32-bit

1

Read Allowed Allowed Allowed

Write Not allowed Not allowed Not allowed

Loading...

Loading...