MPC5604B/C Microcontroller Reference Manual, Rev. 8

860 Freescale Semiconductor

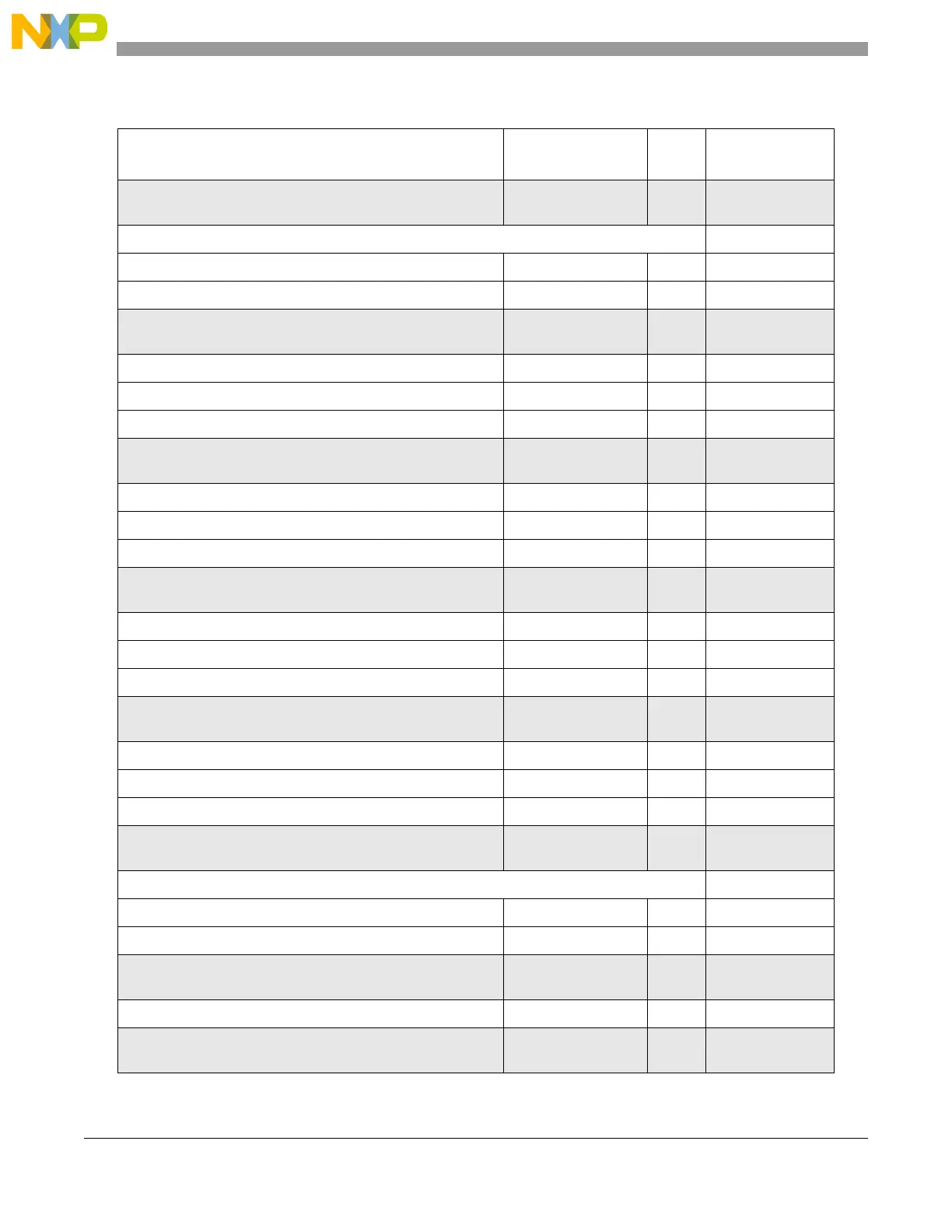

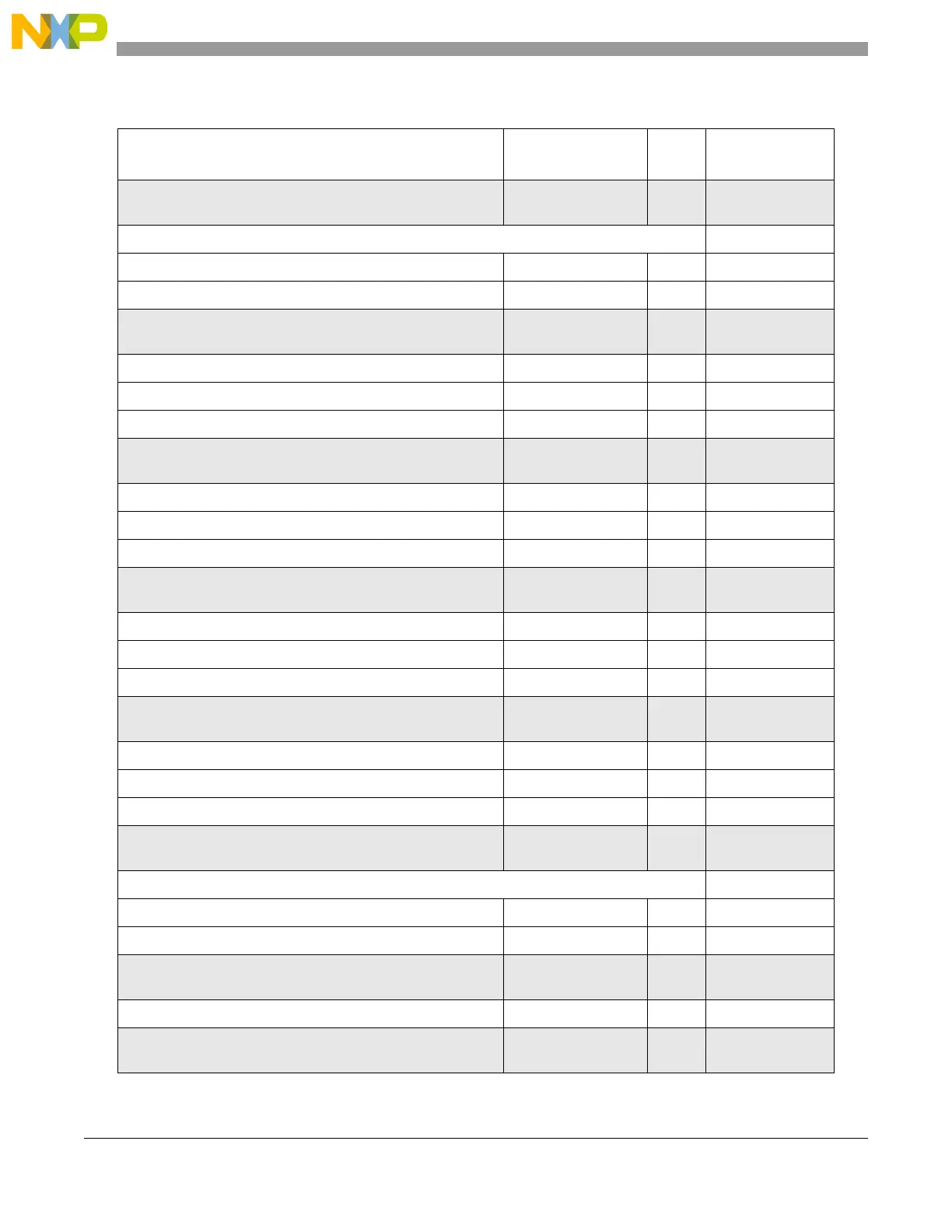

Reserved — — (Base + 0x0018) –

0xFFF3_BFFF

STM 0xFFF3_C000

Control Register STM_CR 32-bit Base + 0x0000

STM Count Register STM_CNT 32-bit Base + 0x0004

Reserved — — Base + (0x0008 –

0x000F)

STM Channel 0 Control Register STM_CCR0 32-bit Base + 0x00010

STM Channel 0 Interrupt Register STM_CIR0 32-bit Base + 0x00014

STM Channel 0 Compare Register STM_CMP0 32-bit Base + 0x00018

Reserved — — Base + (0x001C –

0x001F)

STM Channel 1 Control Register STM_CCR1 32-bit Base + 0x00020

STM Channel 1 Interrupt Register STM_CIR1 32-bit Base + 0x00024

STM Channel 1 Compare Register STM_CMP1 32-bit Base + 0x00028

Reserved — — Base + (0x002C –

0x002F)

STM Channel 2 Control Register STM_CCR2 32-bit Base + 0x00030

STM Channel 2 Interrupt Register STM_CIR2 32-bit Base + 0x00034

STM Channel 2 Compare Register STM_CMP2 32-bit Base + 0x00038

Reserved — — Base + (0x003C –

0x003F)

STM Channel 3 Control Register STM_CCR3 32-bit Base + 0x00040

STM Channel 3 Interrupt Register STM_CIR3 32-bit Base + 0x00044

STM Channel 3 Compare Register STM_CMP3 32-bit Base + 0x00048

Reserved — — Base + (0x003C –

0x03FFF)

ECSM 0xFFF4_0000

Processor Core Type ECSM_PCT 16-bit Base + 0x0000

SOC-Defined Platform Revision ECSM_REV 16-bit Base + 0x0002

Reserved — — Base + (0x0004 –

0x0007)

IPS On-Platform Module Configuration ECSM_IMC 32-bit Base + 0x0008

Reserved — — Base + (0x000C –

0x0012)

Table A-2. Detailed register map (continued)

Register description Register name

Used

size

Address

Loading...

Loading...