MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 367

Reading the IBDR will return the last byte received while the I

2

C is configured in either master receive or

slave receive modes. The IBDR does not reflect every byte that is transmitted on the I

2

C bus, nor can

software verify that a byte has been written to the IBDR correctly by reading it back.

In master transmit mode, the first byte of data written to IBDR following assertion of MS/SL is used for

the address transfer and should comprise the calling address (in position D7–D1) concatenated with the

required R/W bit (in position D0).

20.3.7 I

2

C Bus Interrupt Config Register (IBIC)

20.4 Functional description

20.4.1 I-Bus protocol

The I

2

C Bus system uses a Serial Data line (SDA) and a Serial Clock Line (SCL) for data transfer. All

devices connected to it must have open drain or open collector outputs. A logical AND function is

exercised on both lines with external pull-up resistors. The value of these resistors is system dependent.

Normally, a standard communication is composed of four parts: START signal, slave address transmission,

data transfer and STOP signal. They are described briefly in the following sections and illustrated in

Figure 20-10.

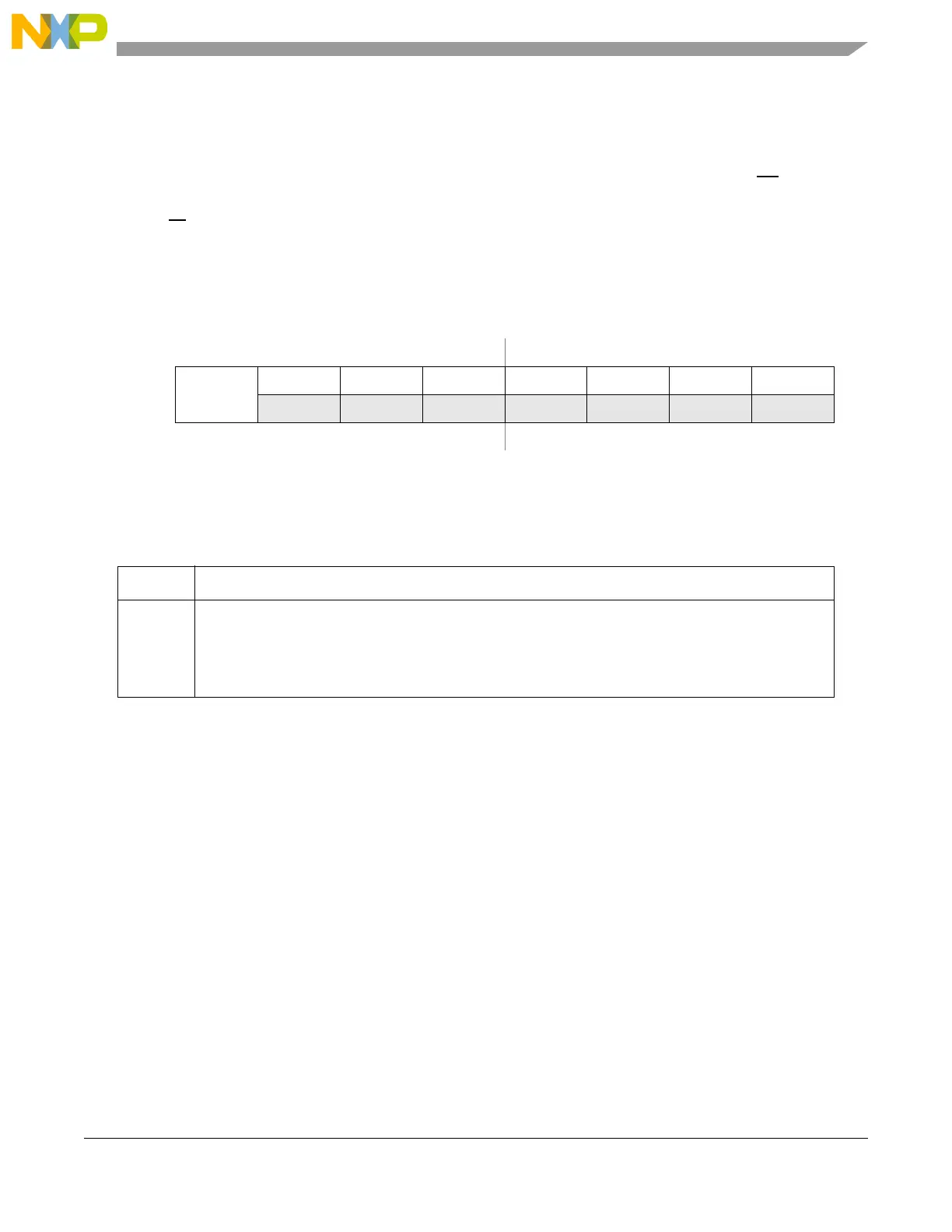

Offset 0x5 Access: Read/write any time

76543210

RBIIE

1

1

This bit cannot be set in reset state, when I2C is in slave mode. It can be set to 1 only when I2C is in Master mode.

This information is missing from the spec.

0000000

W

Reset00000000

Figure 20-9. I

2

C Bus Interrupt Config Register (IBIC)

Table 20-10. IBIC field descriptions

Field Description

BIIE Bus Idle Interrupt Enable bit. This config bit can be used to enable the generation of an interrupt once

the I

2

C bus becomes idle. Once this bit is set, an IBB high-low transition will set the IBIF bit. This feature

can be used to signal to the CPU the completion of a STOP on the I

2

C bus.

1 Bus Idle Interrupts enabled

0 Bus Idle Interrupts disabled

Loading...

Loading...