MPC5604B/C Microcontroller Reference Manual, Rev. 8

764 Freescale Semiconductor

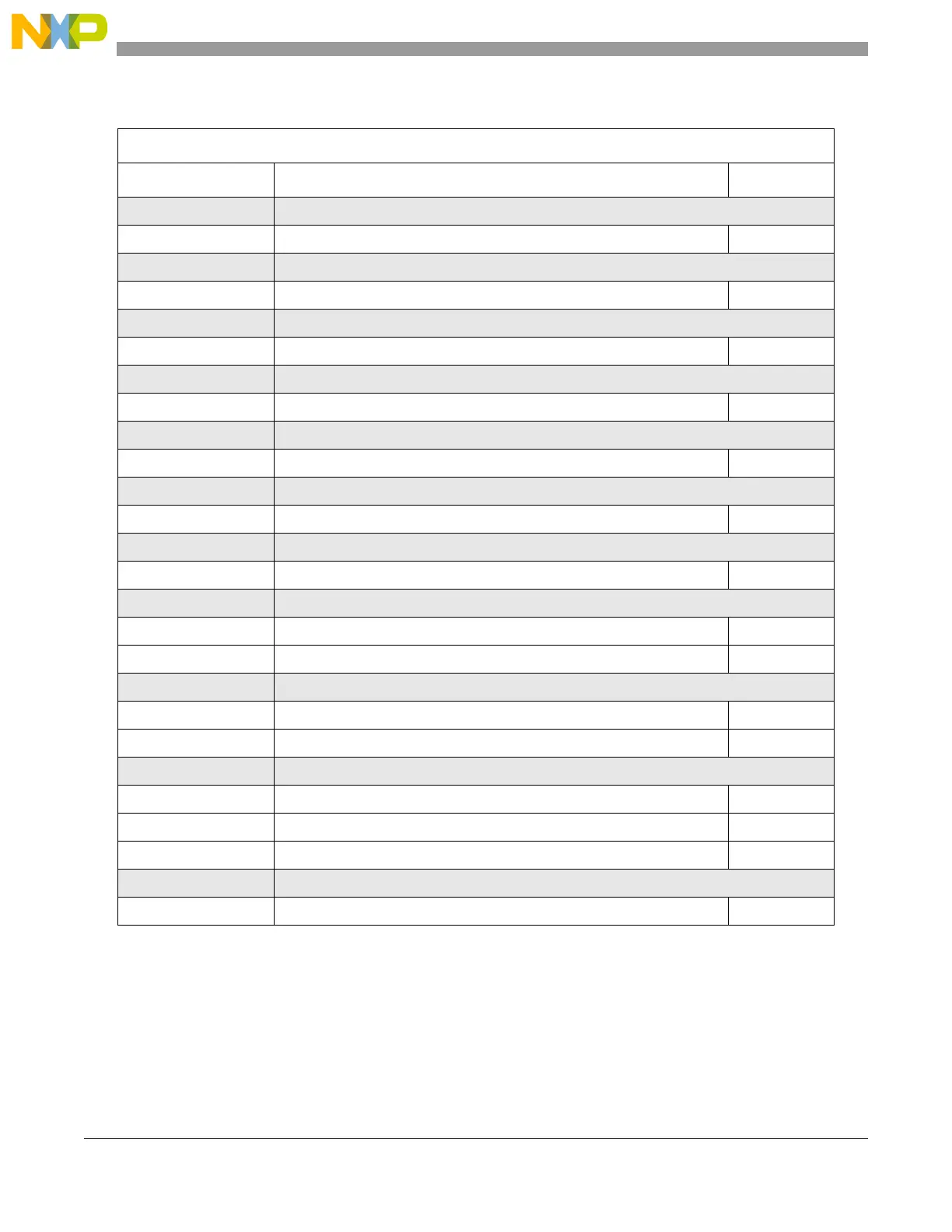

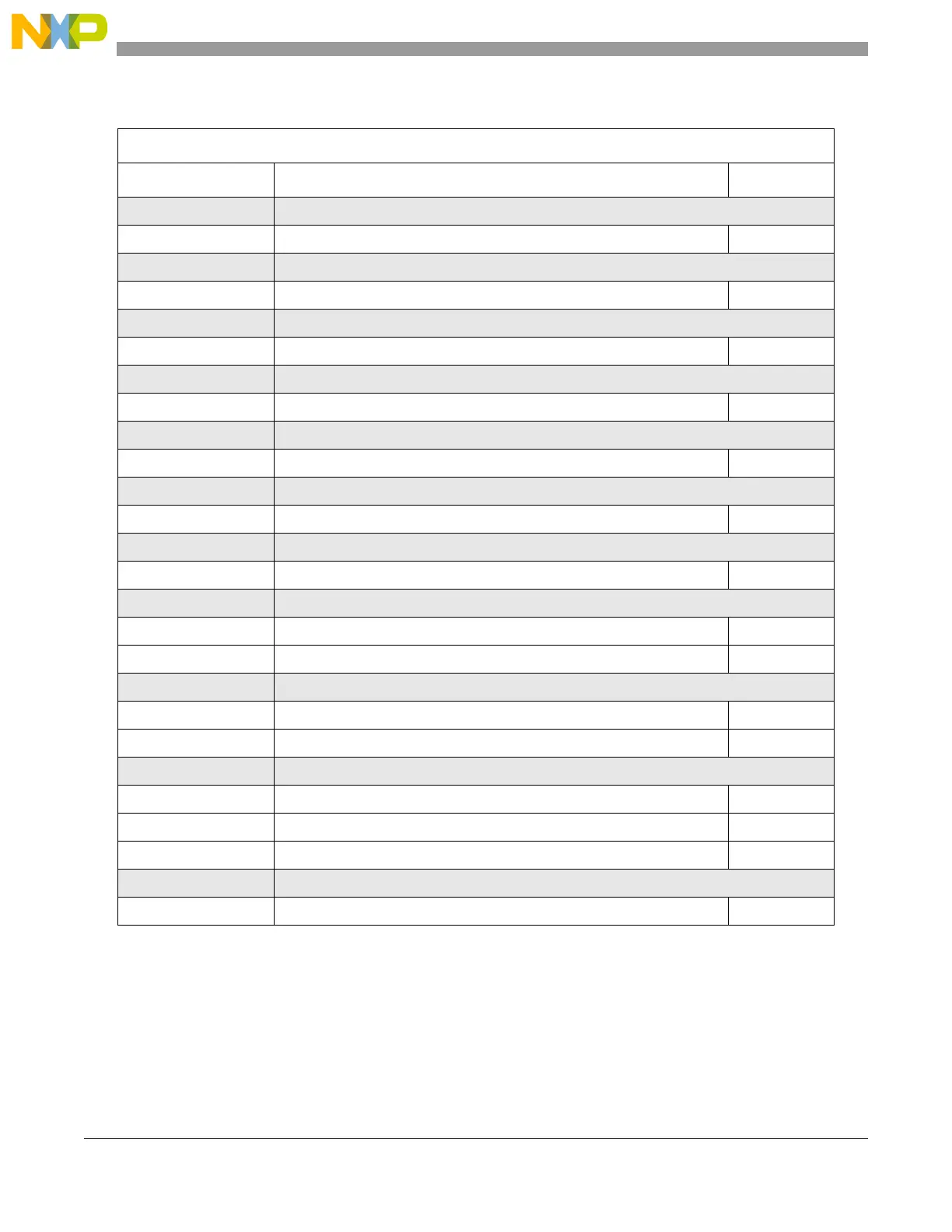

31.4.2 Register description

Attempted accesses to reserved addresses result in an error termination, while attempted writes to

read-only registers are ignored and do not terminate with an error. Unless noted otherwise, writes to the

programming model must match the size of the register, e.g., an n-bit register only supports n-bit writes,

0x0C–0x12 Reserved

0x13 Miscellaneous Wakeup Control Register (MWCR) on page 766

0x14–0x1E Reserved

0x1F Miscellaneous Interrupt Register (MIR) on page 768

0x20–0x23 Reserved

0x24 Miscellaneous User-Defined Control Register (MUDCR) on page 769

0x28–0x42 Reserved

0x43 ECC Configuration Register (ECR) on page 770

0x44–0x46 Reserved

0x47 ECC Status Register (ESR) on page 772

0x48–0x49 Reserved

0x4A ECC Error Generation Register (EEGR) on page 773

0x4C–0x4F Reserved

0x50 Platform Flash ECC Address Register (PFEAR) on page 776

0x54–0x55 Reserved

0x56 Platform Flash ECC Master Number Register (PFEMR) on page 777

0x57 Platform Flash ECC Attributes Register (PFEAT) on page 777

0x58–0x5B Reserved

0x5C Platform Flash ECC Data Register (PFEDR) on page 778

0x60 Platform RAM ECC Address Register (PREAR) on page 779

0x64 Reserved

0x65 Platform RAM ECC Syndrome Register (PRESR) on page 779

0x66 Platform RAM ECC Master Number Register (PREMR) on page 781

0x67 Platform RAM ECC Attributes Register (PREAT) on page 782

0x68–0x6B Reserved

0x6C Platform RAM ECC Data Register (PREDR) on page 783

Table 31-1. ECSM memory map (continued)

Base address: 0xFFF4_0000

Address offset Register Location

Loading...

Loading...