MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 781

31.4.2.7.10 Platform RAM ECC Master Number Register (PREMR)

The PREMR is a 4-bit register for capturing the XBAR bus master number of the last, properly-enabled

ECC event in the SRAM memory. Depending on the state of the ECC Configuration Register, an ECC

event in the SRAM causes the address, attributes and data associated with the access to be loaded into the

PREAR, PRESR, PREMR, PREAT and PREDR registers, and the appropriate flag (R1BC or RNCE) in

the ECC Status Register to be asserted.

See the XBAR chapter of this reference manual for a listing of XBAR bus master numbers.

This register can only be read from the IPS programming model; any attempted write is ignored.

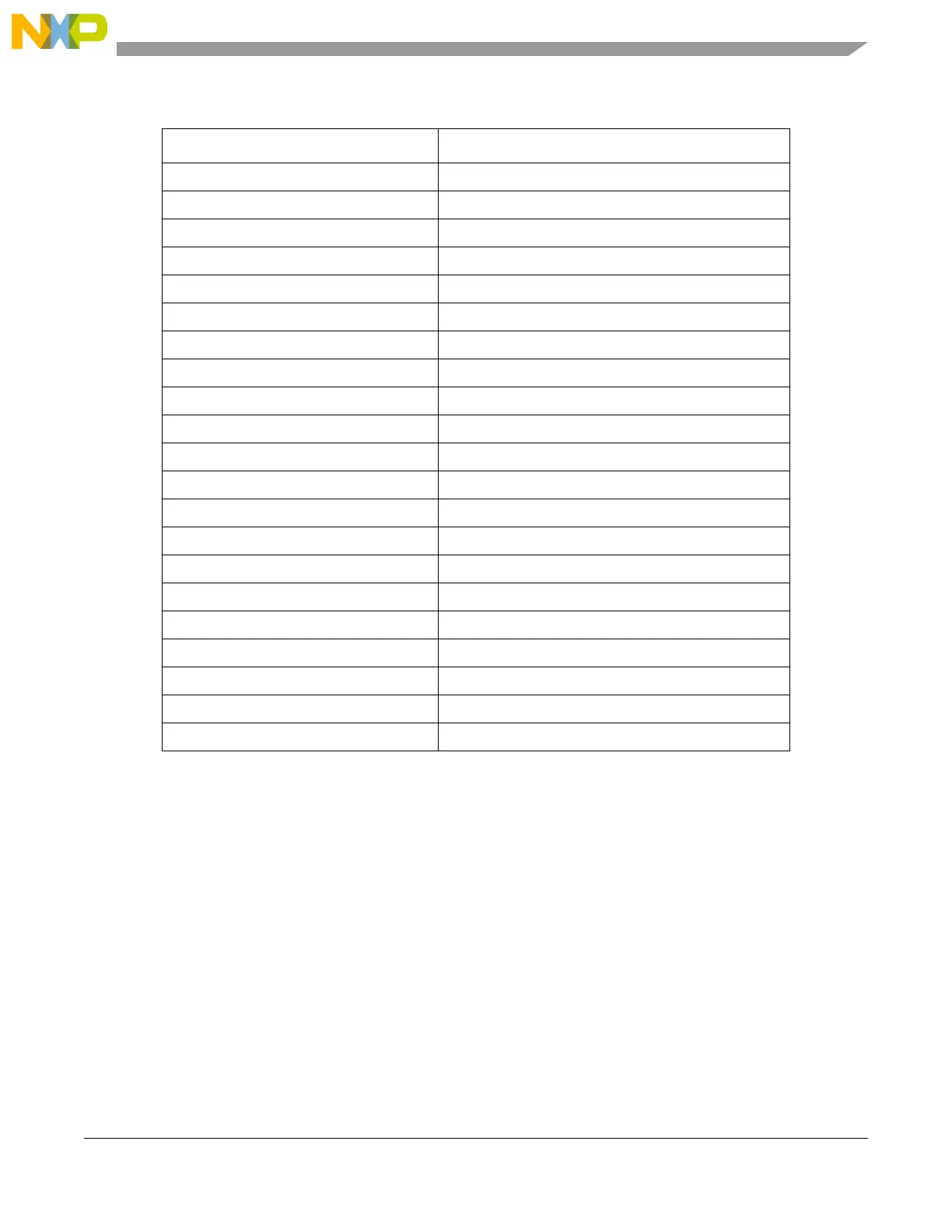

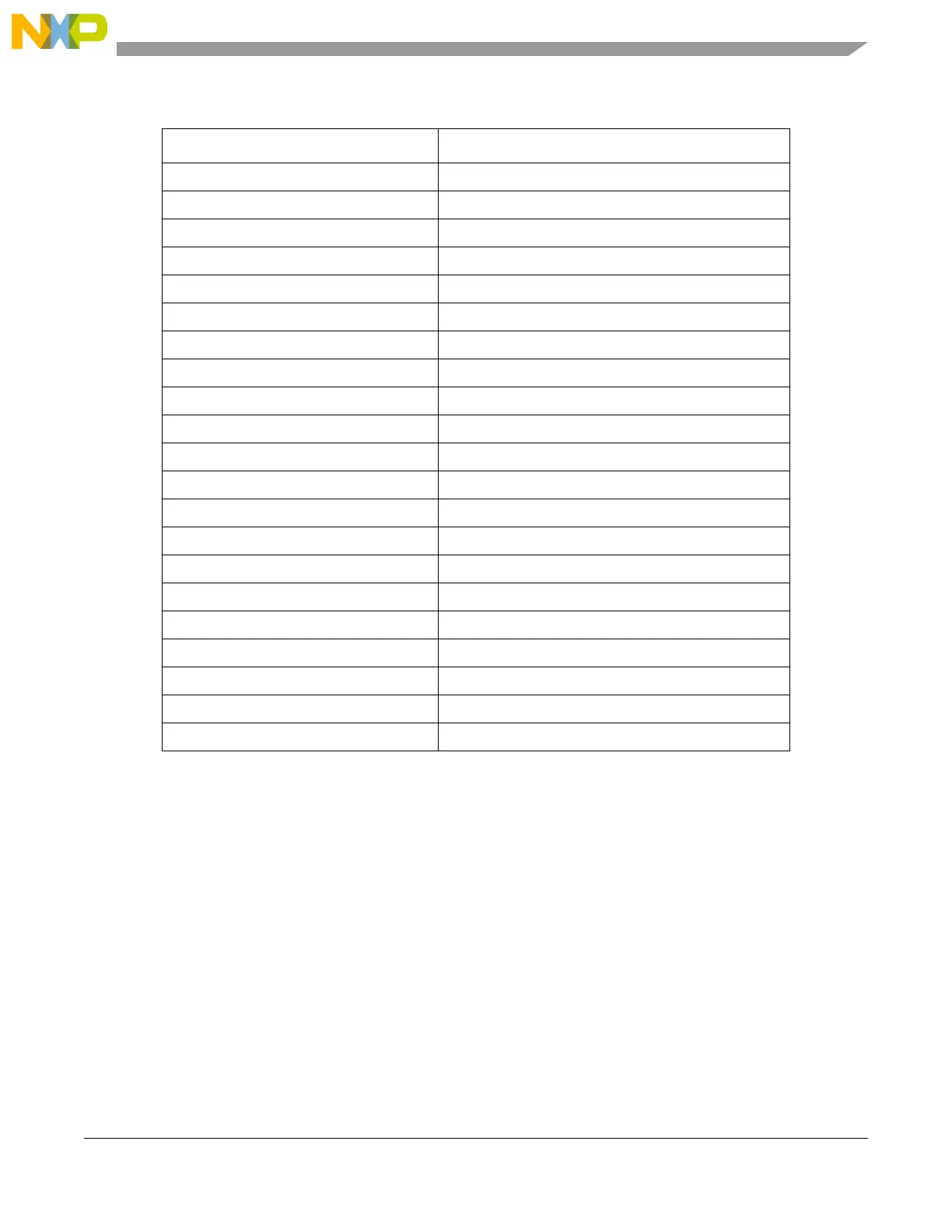

0x28 DATA ODD BANK[17]

0x2a DATA ODD BANK[16

0x2c DATA ODD BANK[15]

0x58 DATA ODD BANK[14]

0x30 DATA ODD BANK[13]

0x32 DATA ODD BANK[12]

0x34 DATA ODD BANK[11]

0x64 DATA ODD BANK[10]

0x38 DATA ODD BANK[9]

0x62 DATA ODD BANK[8]

0x70 DATA ODD BANK[7]

0x60 DATA ODD BANK[6]

0x40 ECC ODD[6]

0x42 DATA ODD BANK[5]

0x44 DATA ODD BANK[4]

0x46 DATA ODD BANK[3]

0x48 DATA ODD BANK[2]

0x4a DATA ODD BANK[1]

0x4c DATA ODD BANK[0]

0x03,0x05........0x4d Multiple bit error

> 0x4d Multiple bit error

Table 31-17. RAM syndrome mapping for single-bit correctable errors (continued)

PRESR[RESR] Data bit in error

Loading...

Loading...