MPC5604B/C Microcontroller Reference Manual, Rev. 8

782 Freescale Semiconductor

31.4.2.7.11 Platform RAM ECC Attributes Register (PREAT)

The PREAT is an 8-bit register for capturing the XBAR bus master attributes of the last, properly-enabled

ECC event in the SRAM memory. Depending on the state of the ECC Configuration Register, an ECC

event in the SRAM causes the address, attributes and data associated with the access to be loaded into the

PREAR, PRESR, PREMR, PREAT and PREDR registers, and the appropriate flag (R1BC or RNCE) in

the ECC Status Register to be asserted.

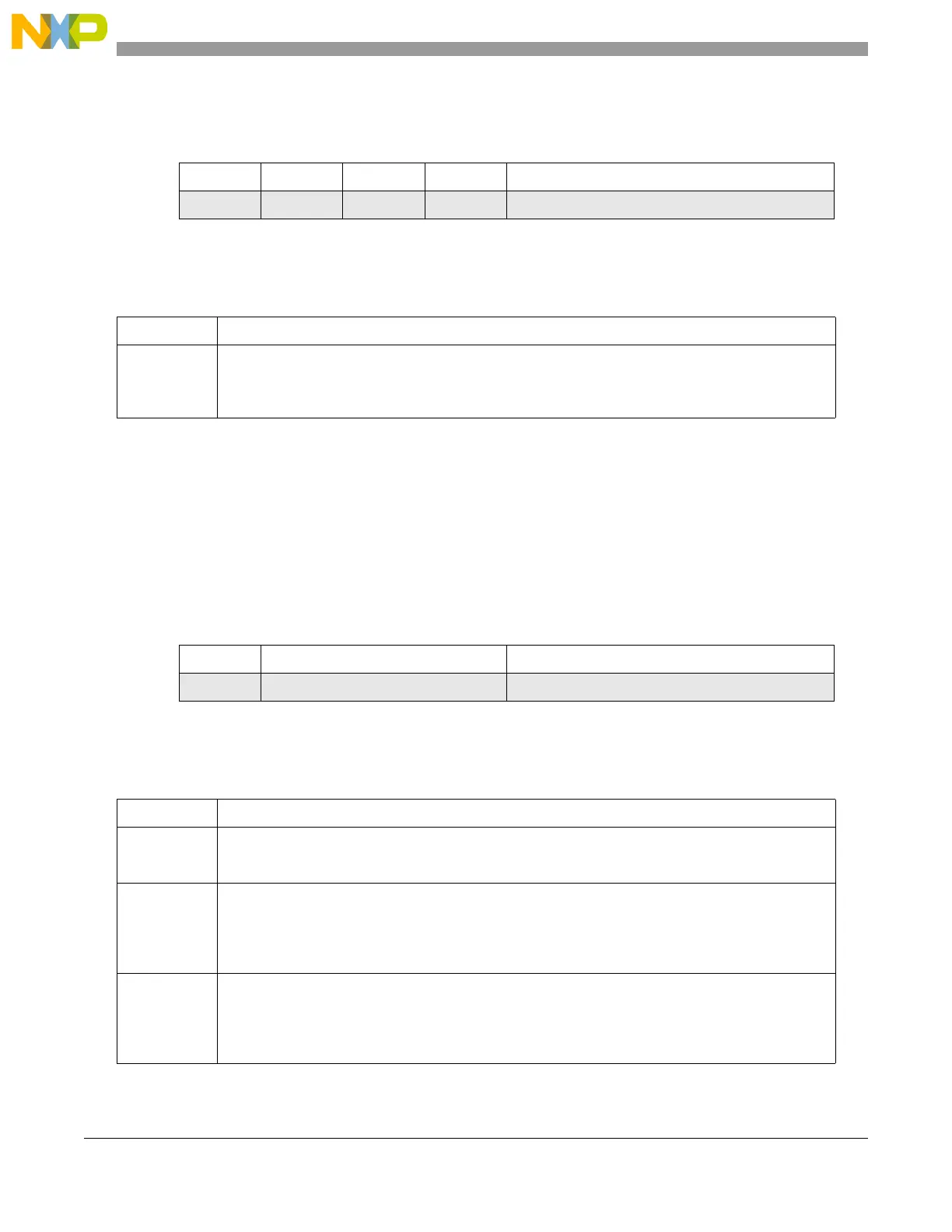

Offset: 0x66 Access: Read

01234567

R0000 REMR

W

Reset:0000––––

Figure 31-16. Platform RAM ECC Master Number Register (PREMR)

Table 31-18. PREMR field descriptions

Field Description

REMR SRAM ECC Master Number Register

This 4-bit register contains the XBAR bus master number of the faulting access of the last,

properly-enabled SRAM ECC event.

See the XBAR chapter of this reference manual for a listing of XBAR bus master numbers.

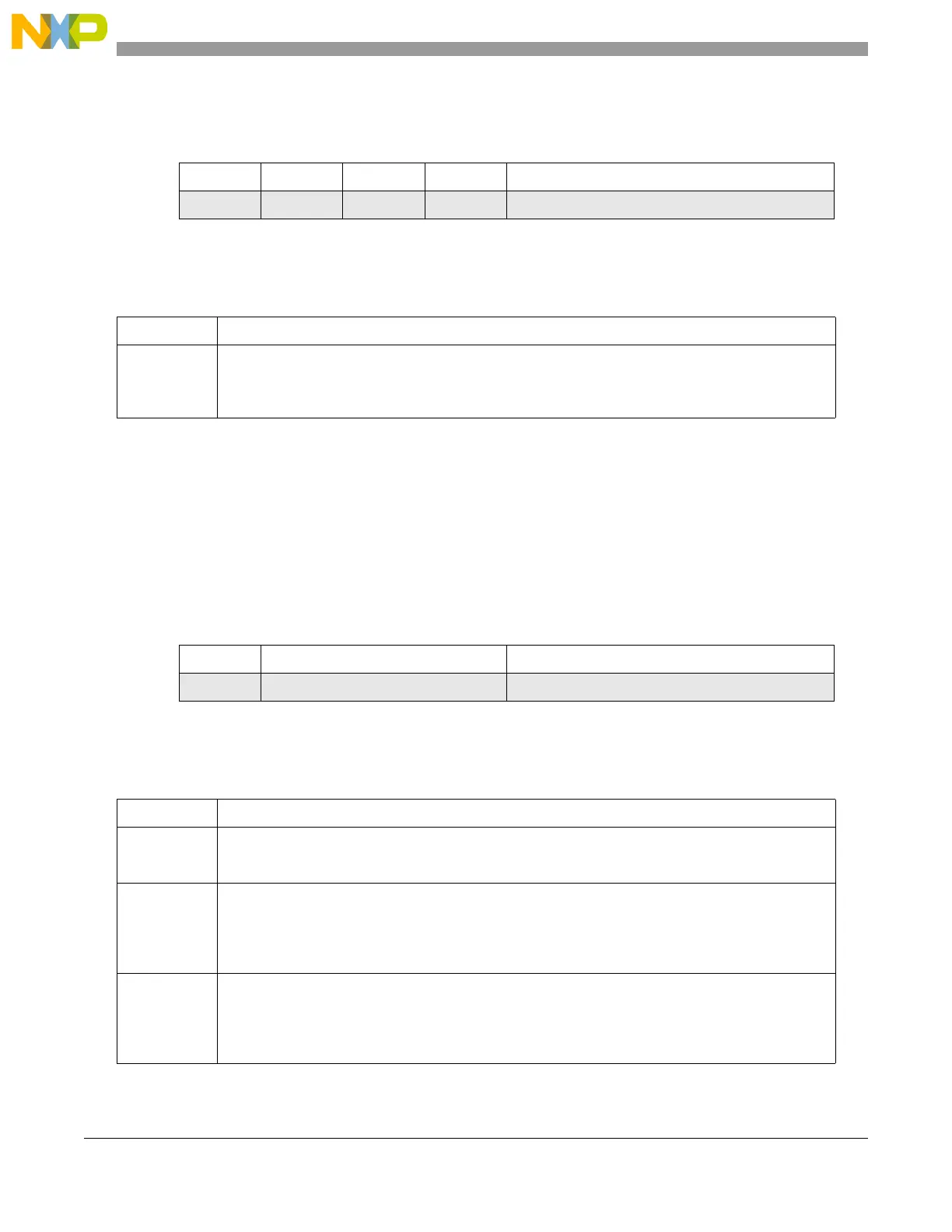

Offset: 0x67 Access: Read

01234567

R WRITE SIZE PROTECTION

W

Reset:––––––––

Figure 31-17. Platform RAM ECC Attributes Register (PREAT)

Table 31-19. PREAT field descriptions

Field Description

WRITE XBAR HWRITE

0 XBAR read access

1 XBAR write access

SIZE XBAR HSIZE[2:0]

000 8-bit XBAR access

001 16-bit XBAR access

010 32-bit XBAR access

1xx Reserved

PROTECTION XBAR HPROT[3:0]

Protection[3]: Cacheable 0 = Non-cacheable, 1 = Cacheable

Protection[2]: Bufferable 0 = Non-bufferable, 1 = Bufferable

Protection[1]: Mode 0 = User mode, 1 = Supervisor mode

Protection[0]: Type 0 = I-Fetch, 1 = Data

Loading...

Loading...