MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 635

Each event has a dedicated configuration register (CTU_EVTCFGR). These registers store a channel

number which is used to communicate which channel needs to be converted.

In case several events are pending for ADC request, the priority is managed according to the timer event

index. The lowest index has the highest priority. Once an event has been serviced (conversion requested

to ADC) the eMIOS flag is cleared by the CTU and next prior event is handled.

The acknowledgment signal can be forced to ‘1’ by setting the CLR_FLAG bit of the CTU_EVTCFGR

register. These bits are implemented for only those input flags to which PIT flags are connected. Providing

these bits offers the option of clearing PIT flags by software.

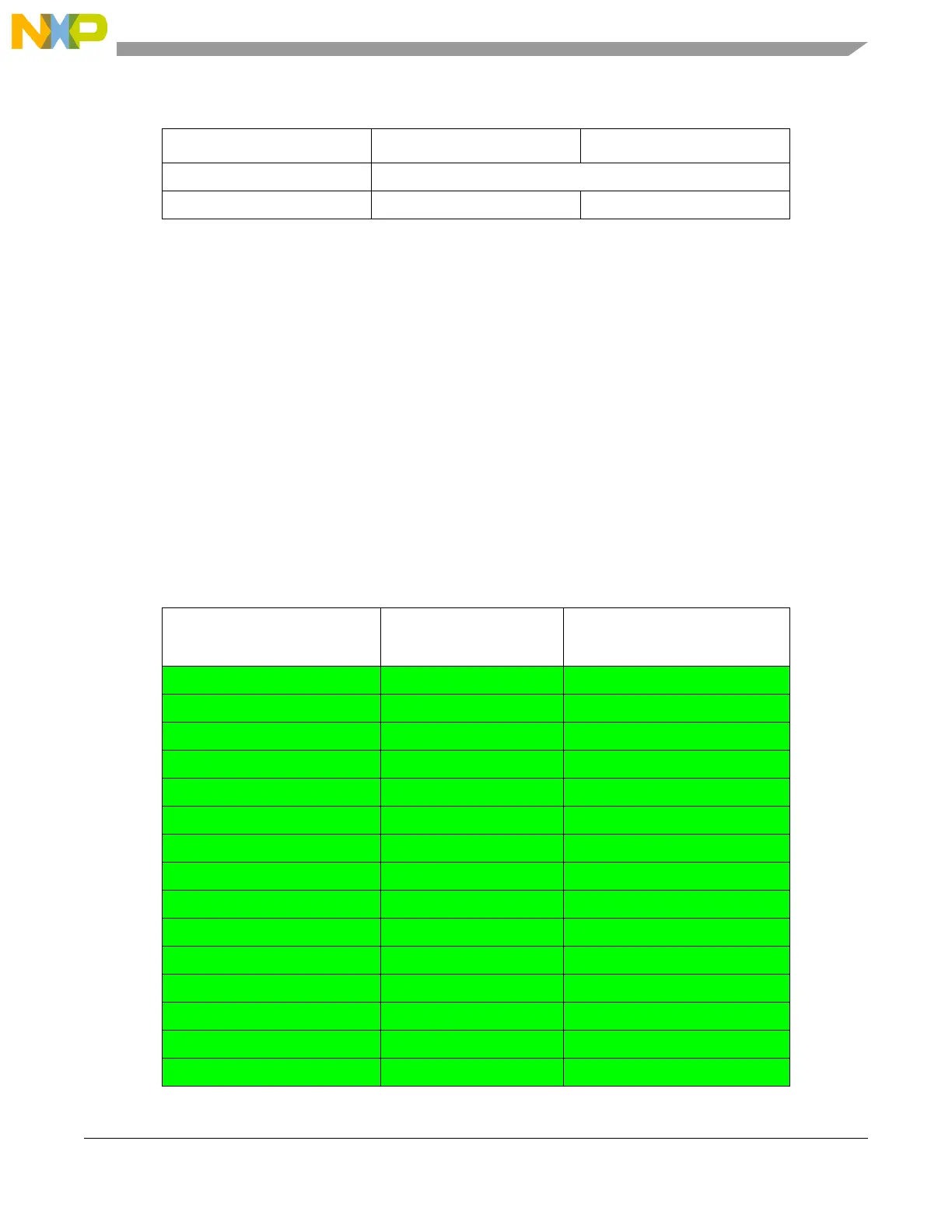

26.5.1 Channel value

The channel value stored in an event configuration register is demultiplexed to 7 bits and then provided to

the ADC.

The mapping of the channel number value to the corresponding ADC channel is provided in Table 26-3.

55 Reserved

56 eMIOS 1 Channel_24

Table 26-4. CTU-to-ADC channel assignment

10-bit ADC signal name 10-bit ADC channel #

Channel number in

CTU_EVTCFGRx

ADC_P[0] CH0 0

ADC_P[1] CH1 1

ADC_P[2] CH2 2

ADC_P[3] CH3 3

ADC_P[4] CH4 4

ADC_P[5] CH5 5

ADC_P[6] CH6 6

ADC_P[7] CH7 7

ADC_P[8] CH8 8

ADC_P[9] CH9 9

ADC_P[10] CH10 10

ADC_P[11] CH11 11

ADC_P[12] CH12 12

ADC_P[13] CH13 13

ADC_P[14] CH14 14

Table 26-3. Trigger source (continued)

CTU trigger No. Module Source

Loading...

Loading...