MPC5604B/C Microcontroller Reference Manual, Rev. 8

478 Freescale Semiconductor

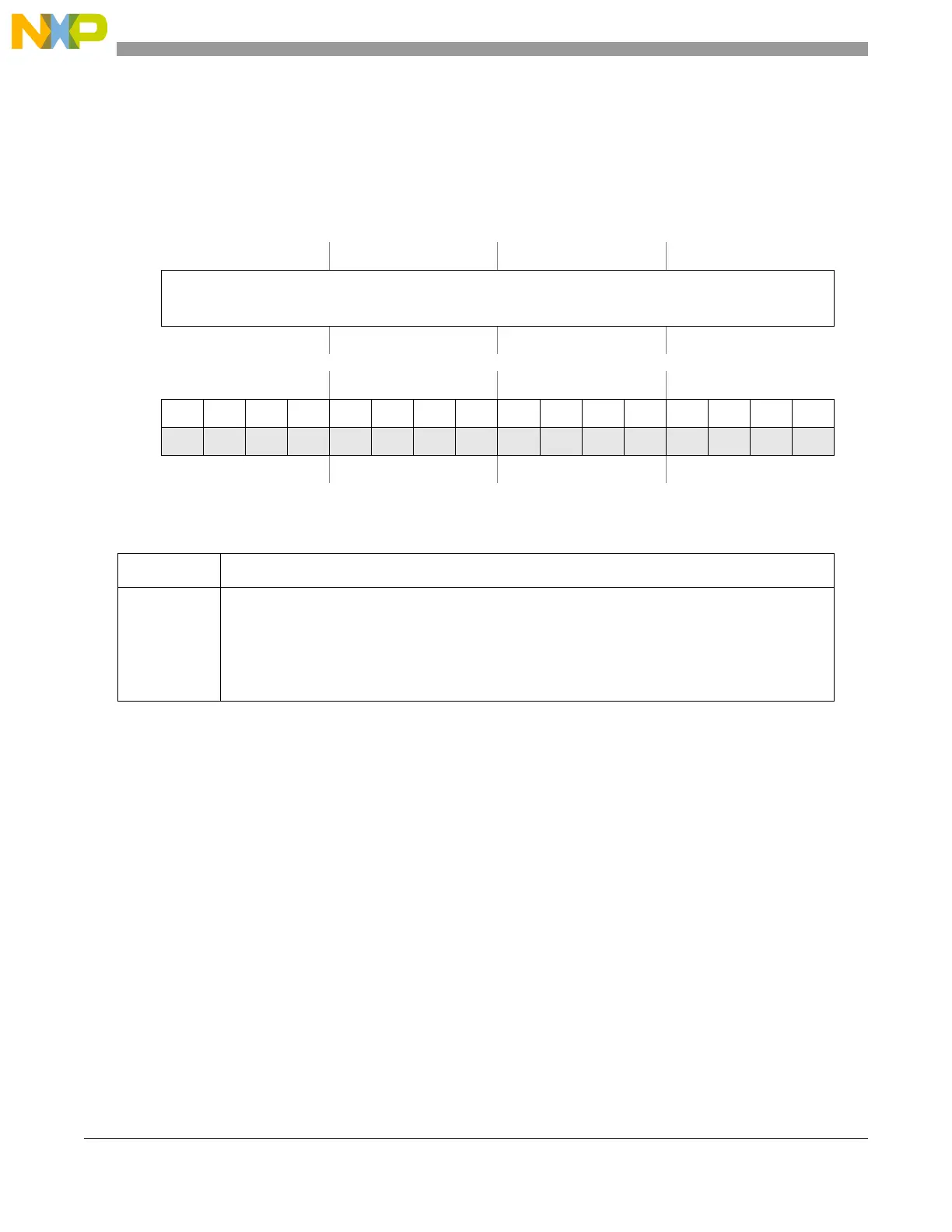

23.5.3 DSPI Transfer Count Register (DSPIx_TCR)

The DSPIx_TCR contains a counter that indicates the number of SPI transfers made. The transfer counter

is intended to assist in queue management. The user must not write to the DSPIx_TCR while the DSPI is

running.

23.5.4 DSPI Clock and Transfer Attributes Registers 0–5 (DSPIx_CTARn)

The DSPI modules each contain six clock and transfer attribute registers (DSPIx_CTARn) which are used

to define different transfer attribute configurations. Each DSPIx_CTAR controls:

•Frame size

• Baud rate and transfer delay values

• Clock phase

• Clock polarity

• MSB or LSB first

DSPIx_CTARs support compatibility with the QSPI module in the MPC5604B family of MCUs. At the

initiation of an SPI transfer, control logic selects the DSPIx_CTAR that contains the transfer’s attributes.

Do not write to the DSPIx_CTARs while the DSPI is running.

In master mode, the DSPIx_CTARn registers define combinations of transfer attributes such as frame size,

clock phase and polarity, data bit ordering, baud rate, and various delays. In slave mode, a subset of the bit

Offset: 0x08 Access: Read/write

0123456789101112131415

R

SPI_TCNT

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0000000000000000

W

Reset0000000000000000

Figure 23-4. DSPI Transfer Count Register (DSPIx_TCR)

Table 23-4. DSPIx_TCR field descriptions

Field Description

SPI_TCNT SPI transfer counter

Counts the number of SPI transfers the DSPI makes. The SPI_TCNT field is incremented every time

the last bit of an SPI frame is transmitted. A value written to SPI_TCNT presets the counter to that

value. SPI_TCNT is reset to zero at the beginning of the frame when the CTCNT field is set in the

executing SPI command. The transfer counter ‘wraps around,’ incrementing the counter past 65535

resets the counter to zero.

Loading...

Loading...