MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 599

25.3.4 ADC CTU (Cross Triggering Unit)

25.3.4.1 Overview

The ADC cross triggering unit (CTU) is added to enhance the injected conversion capability of the ADC.

The CTU is triggered by multiple input events (eMIOS and PIT) and can be used to select the channels to

be converted from the appropriate event configuration register. A single channel is converted for each

request. After performing the conversion, the ADC returns the result on internal bus.

The CTU can be enabled by setting MCR[CTUEN].

The CTU and the ADC are synchronous with the peripheral set 3 clock in both cases.

25.3.4.2 CTU in trigger mode

In CTU trigger mode, normal and injected conversions triggered by the CPU are still enabled.

Once the CTU event configuration register (CTU_EVTCFGRx) is configured and the corresponding

trigger from the eMIOS or PIT is received, the conversion starts. The MSR[CTUSTART] is set

automatically at this point and it is also automatically reset when the CTU triggered conversion is

completed.

If an injected conversion (programmed by the user by setting the JSTART bit) is ongoing and CTU

conversion is triggered, then the injected channel conversion chain is aborted and only the CTU triggered

conversion proceeds. By aborting the injected conversion, the MSR[JSTART] is reset. That abort is

signalled through the status bit MSR[JABORT].

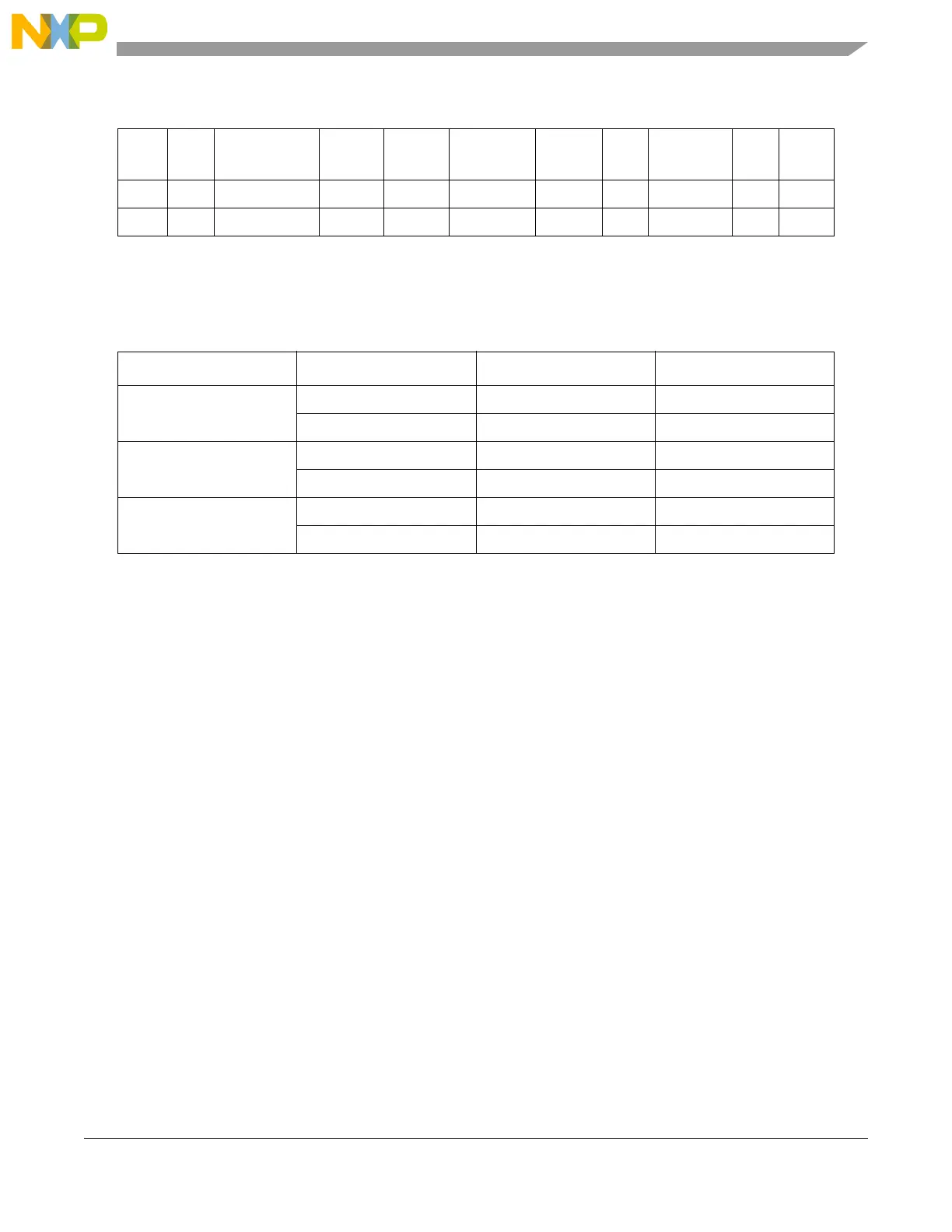

16 0.063 9 1 0.500 8.000 1 0.625 0 1.188 19.000

32 0.031 17 1 0.500 16.000 2 0.625 1 1.156 37.000

1

Where: INPSAMPLE 3

2

Where: INPSAMP 6, N = 0.5; INPSAMP > 6, N = 1

3

Where: T

sample

= (INPSAMP-N)T

ck

; Must be 500 ns

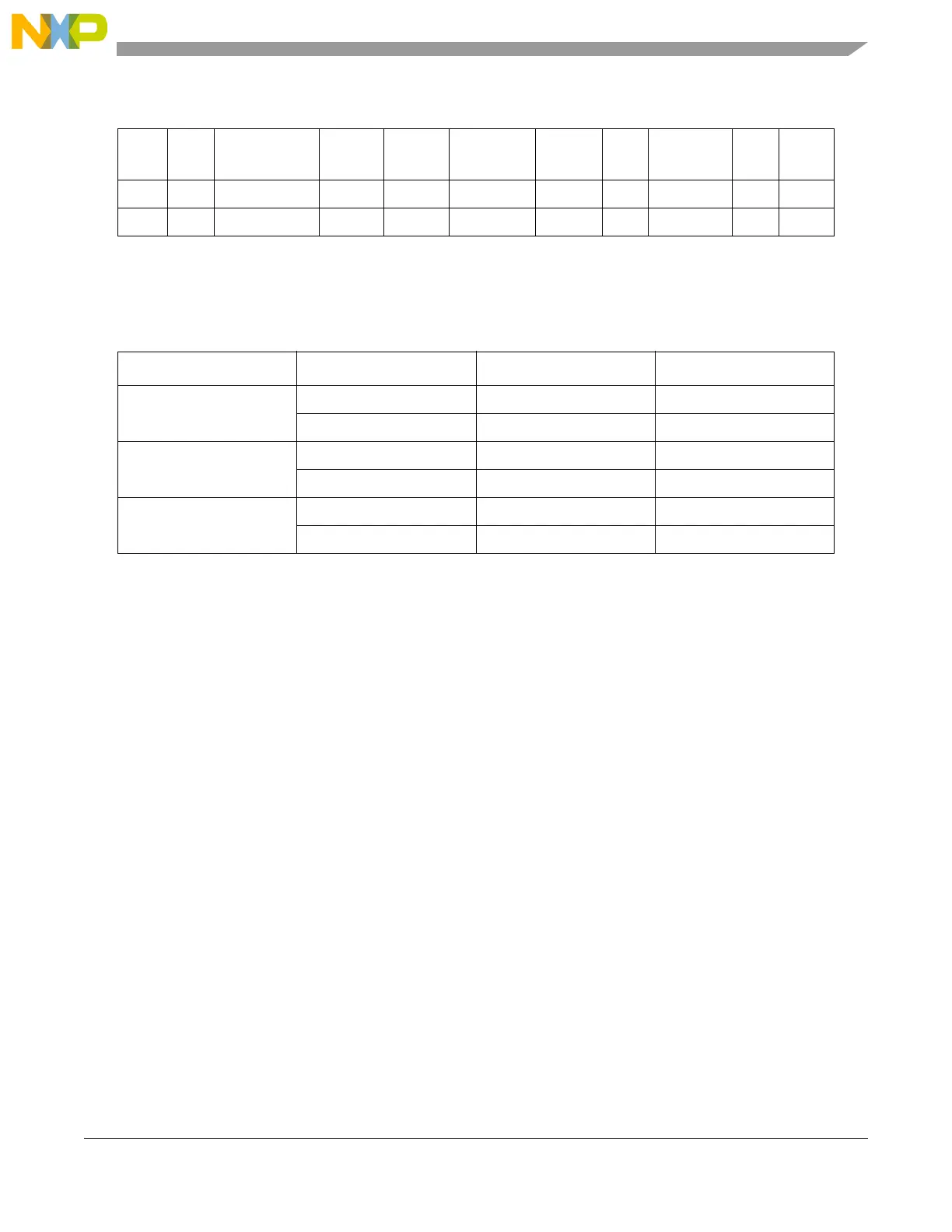

Table 25-3. Max/Min ADC_clk frequency and related configuration settings at 5 V / 3.3 V for ADC_0

INPCMP INPLATCH Max f

ADC_clk

Min f

ADC_clk

00/01 0 20+4% 6

1——

10 0 — —

132+4%6

11 0 — —

132+4%9

Table 25-2. ADC sampling and conversion timing at 5 V / 3.3 V for ADC_0 (continued)

Clock

(MHz)

T

ck

(s)

INPSAMPLE

1

Ndelay

2

T

sample

3

T

sample

/T

ck

INPCMP

T

eval

(s)

INPLATCH

T

conv

(s)

T

conv

/

T

ck

Loading...

Loading...