MPC5604B/C Microcontroller Reference Manual, Rev. 8

234 Freescale Semiconductor

NOTE

Writing a ‘0’ to both NREE0 and NFEE0 disables the NMI functionality

completely (that is, no system wakeup or interrupt will be generated on any

pad activity)!

12.4.4 Wakeup/Interrupt Status Flag Register (WISR)

This register holds the wakeup/interrupt flags.

NWRE0 NMI Wakeup Request Enable

1 A set NIF0 bit or set NOVF0 bit causes a system wakeup request

0 System wakeup requests from the corresponding NIF0 bit are disabled

Note: Software should only enable the NMI after the IVPR/IVOR registers have been configured. This

should be noted when booting from RESET or STANDBY mode as all registers will have been

cleared to their reset state.

NREE0 NMI Rising-edge Events Enable

1 Rising-edge event is enabled

0 Rising-edge event is disabled

NFEE0 NMI Falling-edge Events Enable

1 Falling-edge event is enabled

0 Falling-edge event is disabled

NFE0 NMI Filter Enable

Enable analog glitch filter on the NMI pad input.

1 Filter is enabled

0 Filter is disabled

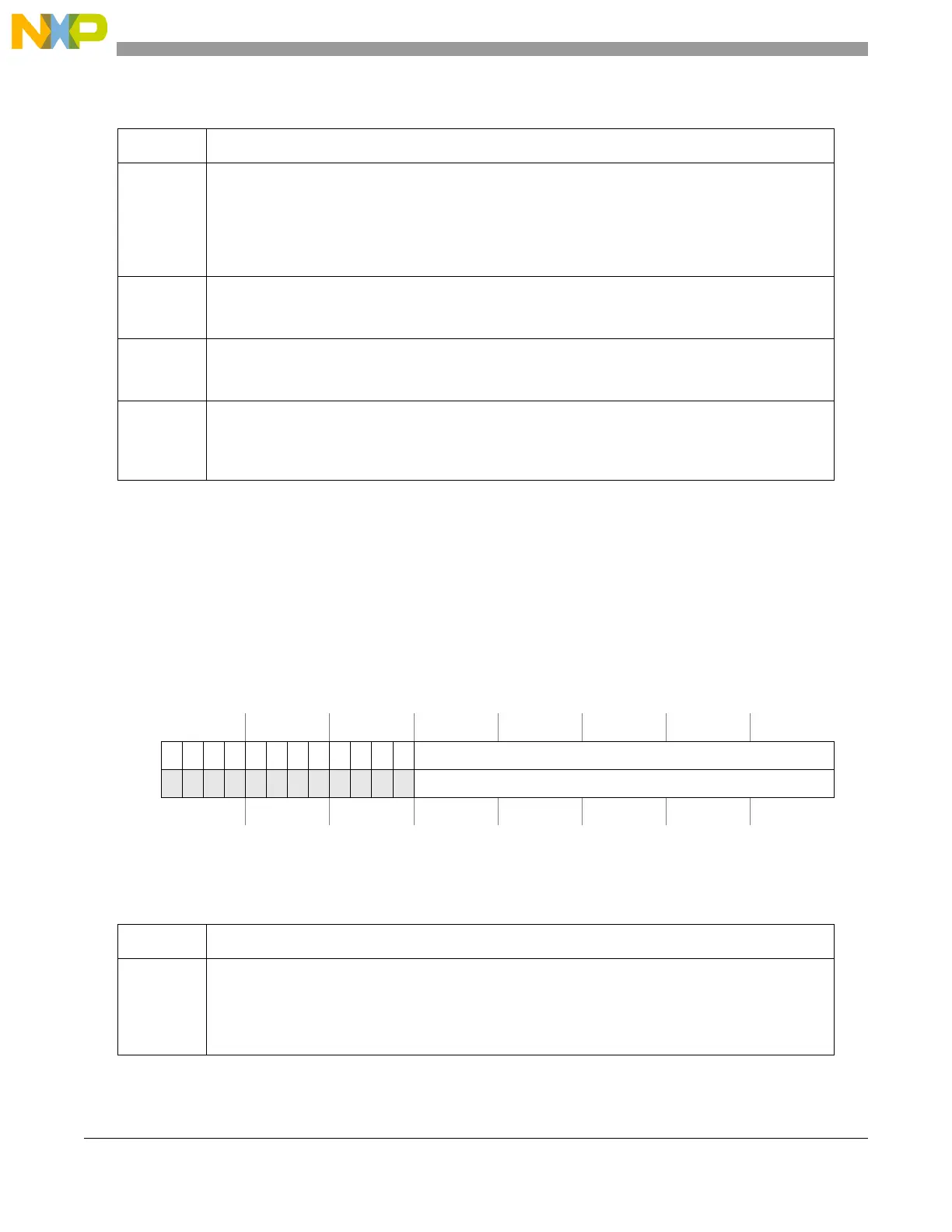

Offset: 0x14 Access: User read/write

012345678910111213141516171819202122232425262728293031

R000000000000 EIF[19:0]

1

1

EIF[18:15] are not available in all 100-pin packages.

W

w1c

Reset00000000000000000000000000000000

Figure 12-4. Wakeup/Interrupt Status Flag Register (WISR)

Table 12-5. WISR field descriptions

Field Description

EIF[x] External Wakeup/Interrupt WKPU[x] Status Flag

This flag can be cleared only by writing a 1. Writing a 0 has no effect. If enabled (IRER[x]), EIF[x]

causes an interrupt request.

1 An event as defined by WIREER and WIFEER has occurred

0 No event has occurred on the pad

Table 12-4. NCR field descriptions (continued)

Field Description

Loading...

Loading...