MPC5604B/C Microcontroller Reference Manual, Rev. 8

622 Freescale Semiconductor

25.4.6 Conversion timing registers CTR[0..2]

CTR0 = associated to internal precision channels (from 0 to 15)

CTR1 = associated to standard channels (from 32 to 47)

CTR2 = associated to external multiplexed channels (from 64 to 95)

25.4.7 Mask registers

25.4.7.1 Introduction

These registers are used to program which of the 96 input channels must be converted during Normal and

Injected conversion.

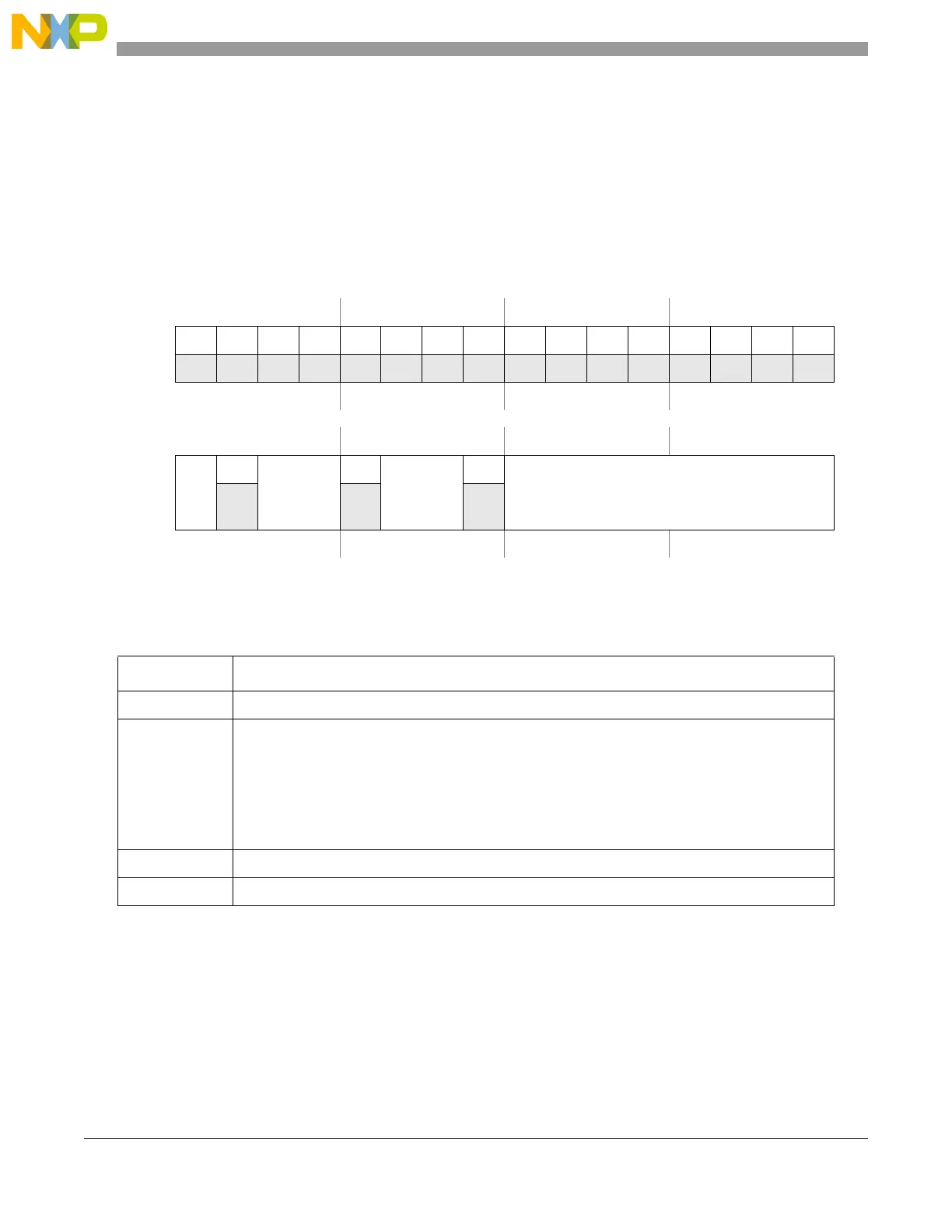

Address:

Base + 0x0094 (CTR0)

Base + 0x0098 (CTR1)

Base + 0x009C (CTR2)

Access: User read/write

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

INPLATCH

0

OFFSHIFT

1

1

Available only on CTR0

0

INPCMP

0

INPSAMP

W

Reset0000001000000101

Figure 25-26. Conversion timing registers CTR[0..2]

Table 25-19. CTR field descriptions

Field Description

INPLATCH Configuration bit for latching phase duration

OFFSHIFT Configuration for offset shift characteristic

00 No shift (that is the transition between codes 000h and 001h) is reached when the A

VIN

(analog input voltage) is equal to 1 LSB.

01 Transition between code 000h and 001h is reached when the A

VIN

is equal to1/2 LSB

10 Transition between code 00h and 001h is reached when the A

VIN

is equal to 0

11 Not used

Note: Available only on CTR0

INPCMP Configuration bits for comparison phase duration

INPSAMP Configuration bits for sampling phase duration

Loading...

Loading...