MPC5604B/C Microcontroller Reference Manual, Rev. 8

116 Freescale Semiconductor

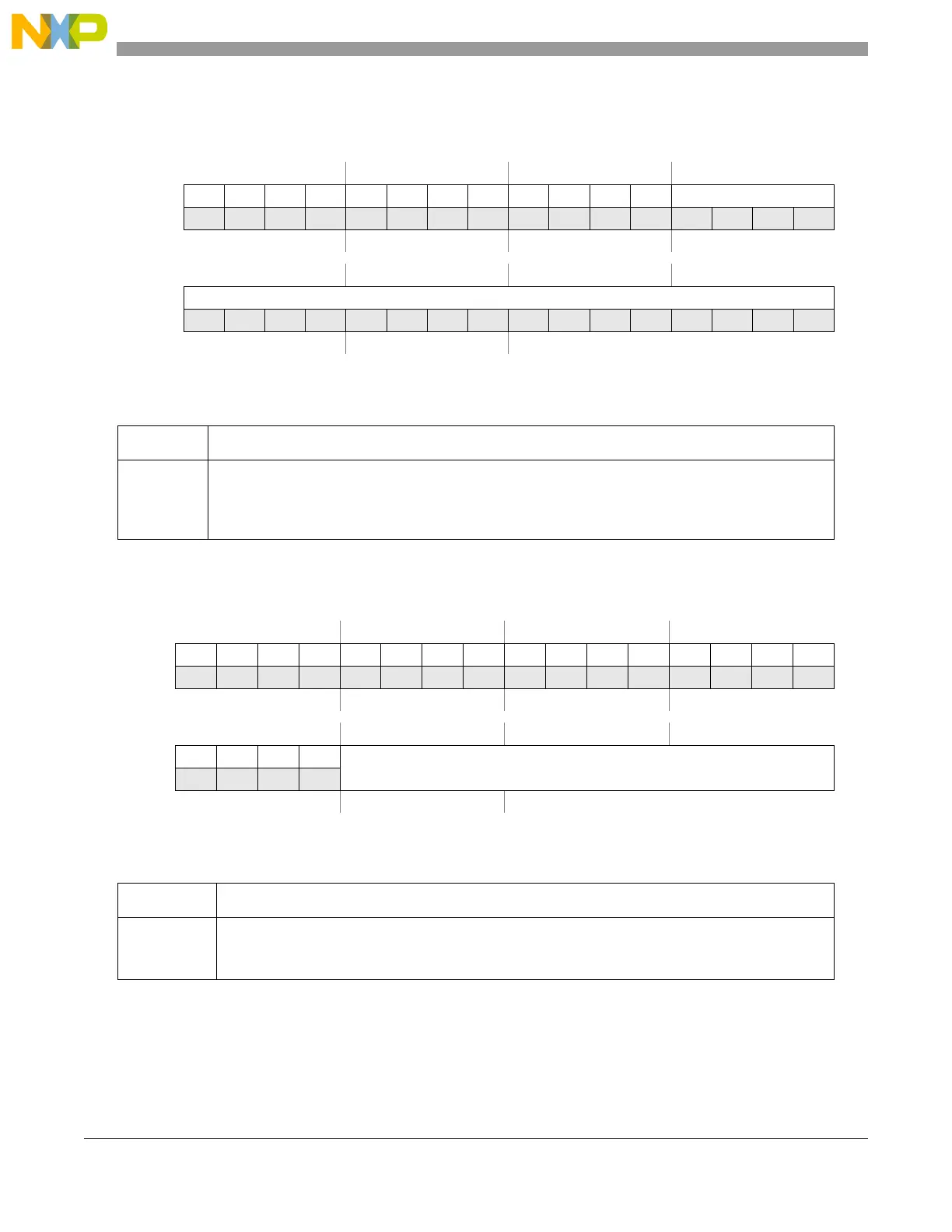

6.8.5.2 Frequency Display Register (CMU_FDR)

.

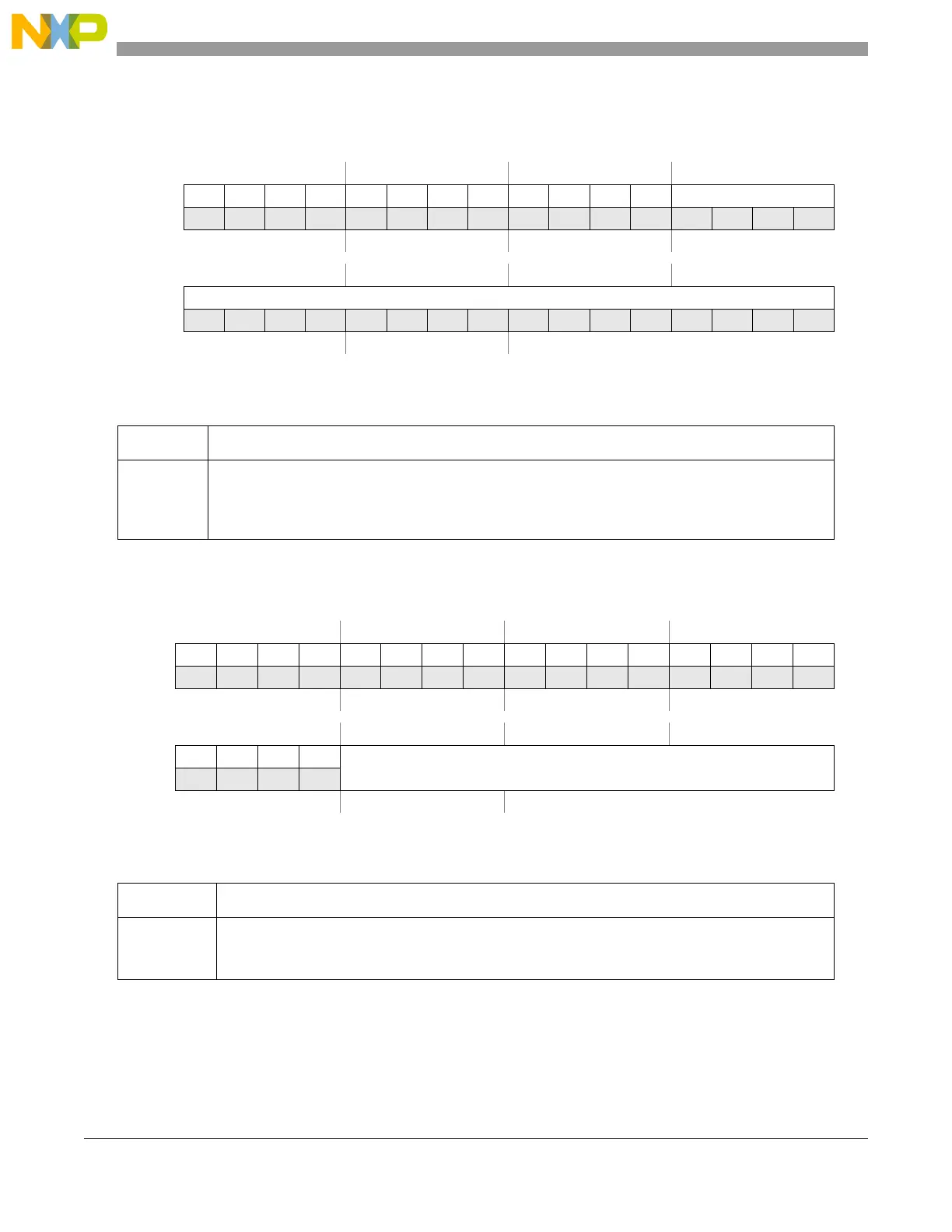

6.8.5.3 High Frequency Reference Register FMPLL (CMU_HFREFR)

Offset:

0x04 Access: Read-only

0123456789101112131415

R00000000 0 0 0 0 FD[19:16]

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R FD[15:0]

W

Reset0000000000000000

Figure 6-13. Frequency Display Register (CMU_FDR)

Table 6-18. CMU_FDR field descriptions

Field Description

FD Measured frequency bits.

This register displays the measured frequency f

x

with respect to f

FXOSC

. The measured value is given

by the following formula: f

x

= (f

FXOSC

× MD) / n, where n is the value in CMU_FDR register.

Note: x = FIRC, SIRC or SXOSC.

Offset:

0x08 Access: Read/write

0123456789101112131415

R00000000 00000 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0000

HFREF

W

Reset0000111111111111

Figure 6-14. High Frequency Reference Register FMPLL (CMU_HFREFR)

Table 6-19. CMU_HFREFR field descriptions

Field Description

HFREF High Frequency reference value.

This field determines the high reference value for the FMPLL clock. The reference value is given by:

(HFREF 16) × (f

FIRC

4).

Loading...

Loading...