MPC5604B/C Microcontroller Reference Manual, Rev. 8

750 Freescale Semiconductor

29.6.3 Access errors

The protection module generates transfer errors under several circumstances. For the area definition refer

to Figure 29-2.

1. If accessing area #1 or area #3, the protection module transfers any access error from the

underlying Module under Protection.

2. If user mode is not allowed, user write attempts to all areas will assert a transfer error and the writes

will be blocked.

3. Access attempts to the reserved area #2 cause a transfer error to be asserted.

4. Access attempts to unimplemented 32-bit registers in area #4 or area #5 cause a transfer error to be

asserted.

5. Attempted writes to a register in area #1 or area #3 with soft lock bit set for any of the affected

bytes causes a transfer error to be asserted and the write is blocked. The complete write operation

to non-protected bytes in this word is ignored.

6. If writing to a soft lock register in area #4 with the hard lock bit being set a transfer error is asserted.

7. Any write operation in any access mode to area #3 while GCR.HLB is set result in a error.

29.7 Reset

The reset state of each individual bit is shown within the Register Description section (See Section 29.5.2,

Register description). In summary, after reset, locking for all MRn registers is disabled. The registers can

be accessed in Supervisor Mode only.

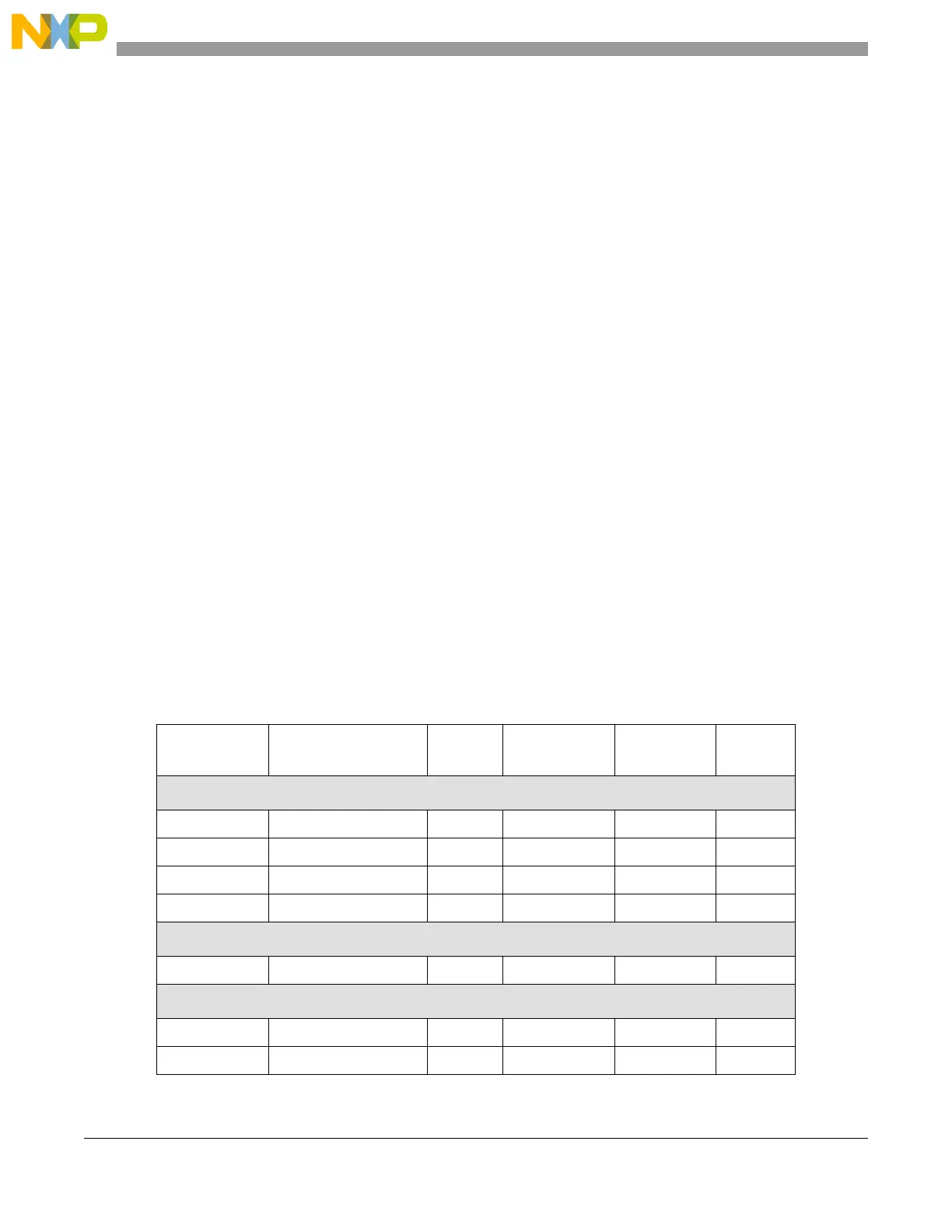

29.8 Protected registers

For MPC5604B the Register Protection module protects the registers shown in Table 29-5.

Table 29-5. Protected registers

Module Register

Protected

size (bits)

Module base

address

Register

offset

Protected

bits

Code flash memory , 4 registers to protect

Code Flash MCR 32 C3F88000 000 bits[0:31]

Code Flash PFCR0 32 C3F88000 01C bits[0:31]

Code Flash PFCR1 32 C3F88000 020 bits[0:31]

Code Flash PFAPR 32 C3F88000 024 bits[0:31]

Data flash memory, 1 register to protect

Data Flash MCR 32 C3F8C000 000 bits[0:31]

SIU lite, 64 registers to protect

SIUL IRER 32 C3F90000 018 bits[0:31]

SIUL IREER 32 C3F90000 028 bits[0:31]

Loading...

Loading...