MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 115

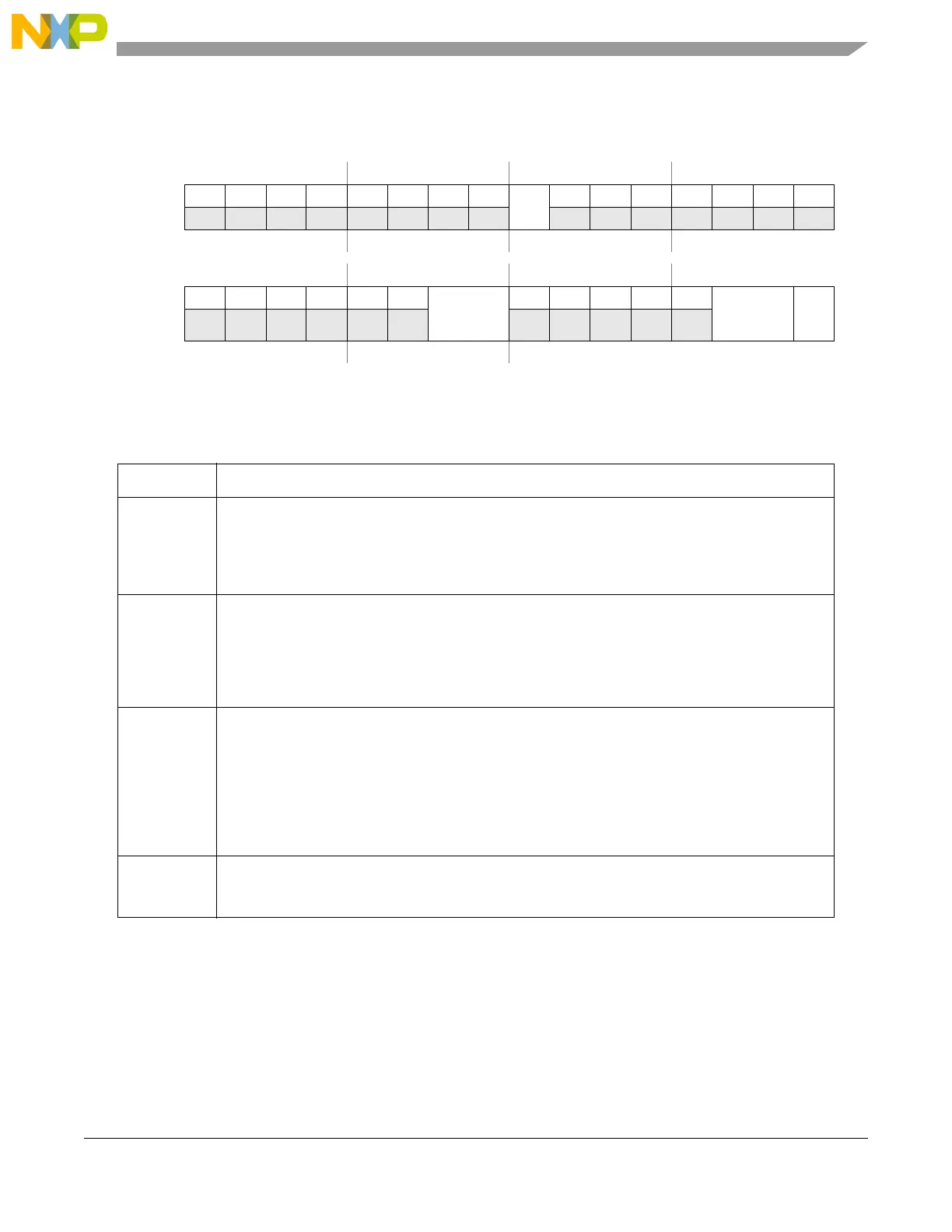

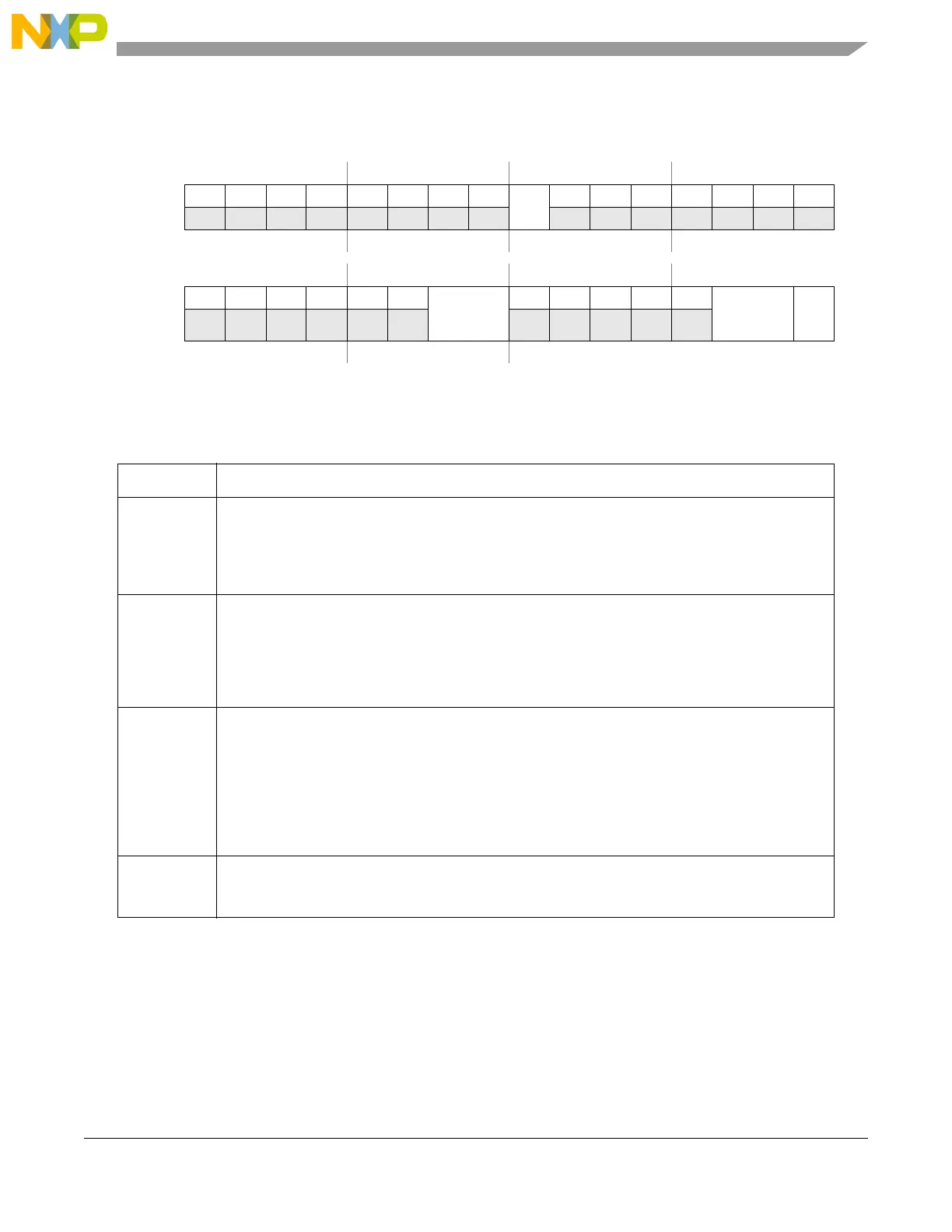

6.8.5.1 Control Status Register (CMU_CSR)

Offset: 0x00 Access: Read/write

0123456789101112131415

R00000000

SFM

1

1

You can read this field, and you can write a value of "1" to it. Writing a "0" has no effect. A reset will also clear this bit.

000

0 000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R000000

CKSEL1

00000

RCDIV

CME_A

W

Reset0000000000000110

Figure 6-12. Control Status Register (CMU_CSR)

Table 6-17. CMU_CSR field descriptions

Field Description

SFM Start frequency measure.

The software can only set this bit to start a clock frequency measure. It is reset by hardware when

the measure is ready in the CMU_FDR register.

0 Frequency measurement completed or not yet started.

1 Frequency measurement not completed.

CKSEL1 Clock oscillator selection bit.

CKSEL1 selects the clock to be measured by the frequency meter.

00 FIRC_clk selected.

01 SIRC_clk selected.

10 SXOSC_clk selected.

11 FIRC_clk selected.

RCDIV RC clock division factor .

These bits specify the RC clock division factor. The output clock is FIRC_clk divided by the factor

2

RCDIV

. This output clock is used to compare with FXOSC_clk for crystal clock monitor feature.The

clock division coding is as follows.

00 Clock divided by 1 (No division)

01 Clock divided by 2

10 Clock divided by 4

11 Clock divided by 8

CME_A FMPLL_0 clock monitor enable.

0 FMPLL_0 monitor disabled.

1 FMPLL_0 monitor enabled.

Loading...

Loading...