MPC5604B/C Microcontroller Reference Manual, Rev. 8

166 Freescale Semiconductor

8.4 Functional Description

8.4.1 Mode Transition Request

The transition from one mode to another mode is normally handled by software by accessing the mode

control ME_MCTL register. But in case of special events, mode transition can be automatically managed

by hardware. In order to switch from one mode to another, the application should access ME_MCTL

register twice by writing

• the first time with the value of the key (0x5AF0) into the KEY bit field and the required target mode

into the TARGET_MODE bit field,

• and the second time with the inverted value of the key (0xA50F) into the KEY bit field and the

required target mode into the TARGET_MODE bit field.

Once a valid mode transition request is detected, the target mode configuration information is loaded from

the corresponding ME_<mode>_MC register. The mode transition request may require a number of cycles

depending on the programmed configuration, and software should check the S_CURRENT_MODE bit

field and the S_MTRANS bit of the global status register ME_GS to verify when the mode has been

correctly entered and the transition process has completed. For a description of valid mode requests, please

refer to Section 8.4.5, “Mode Transition Interrupts“.

Any modification of the mode configuration register of the currently selected mode will not be taken into

account immediately but on the next request to enter this mode. This means that transition requests such

as RUN0…3 RUN0…3, DRUN DRUN, SAFE SAFE, and TEST TEST are considered valid

mode transition requests. As soon as the mode request is accepted as valid, the S_MTRANS bit is set till

the status in the ME_GS register matches the configuration programmed in the respective

ME_<mode>_MC register.

NOTE

It is recommended that software poll the S_MTRANS bit in the ME_GS

register after requesting a transition to HALT, STOP, or STANDBY modes.

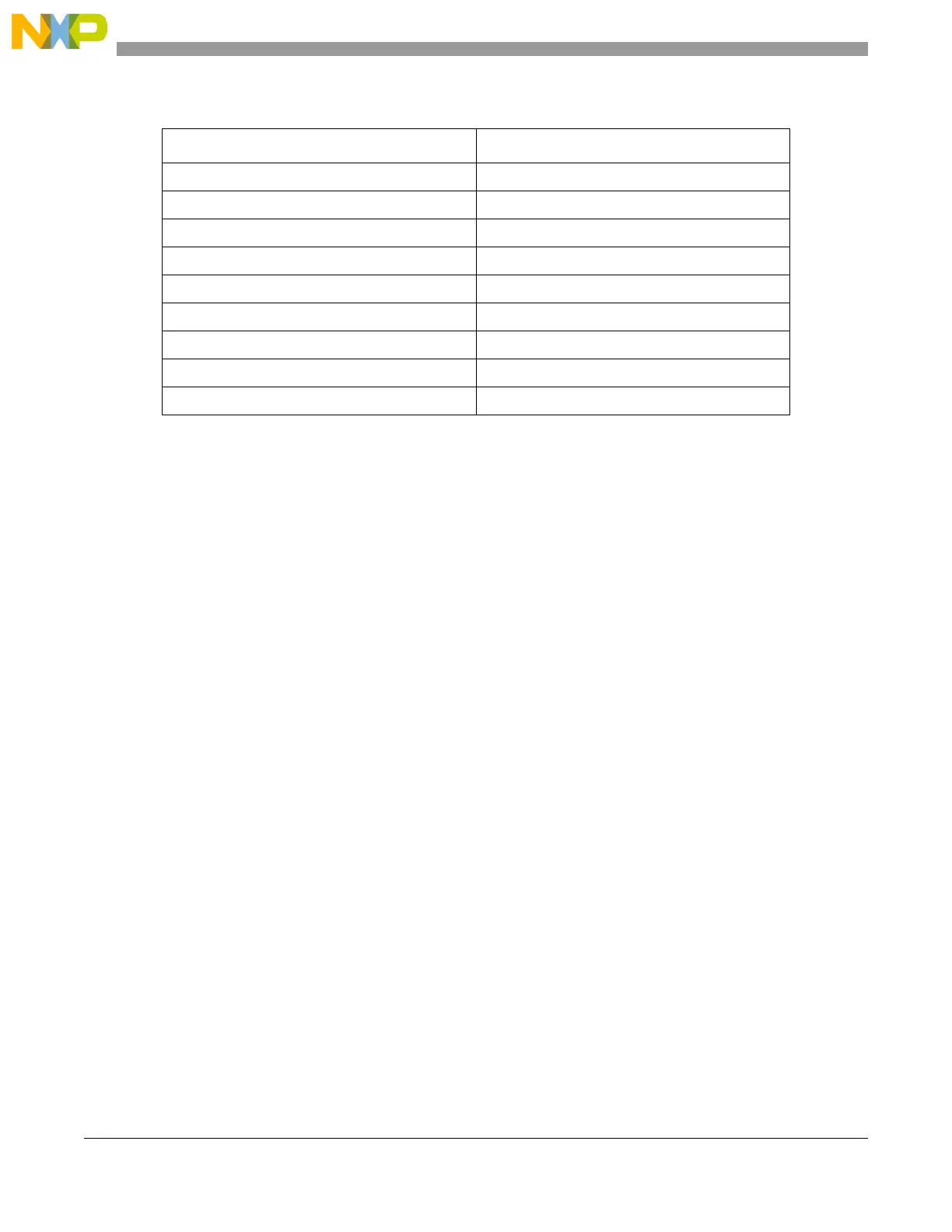

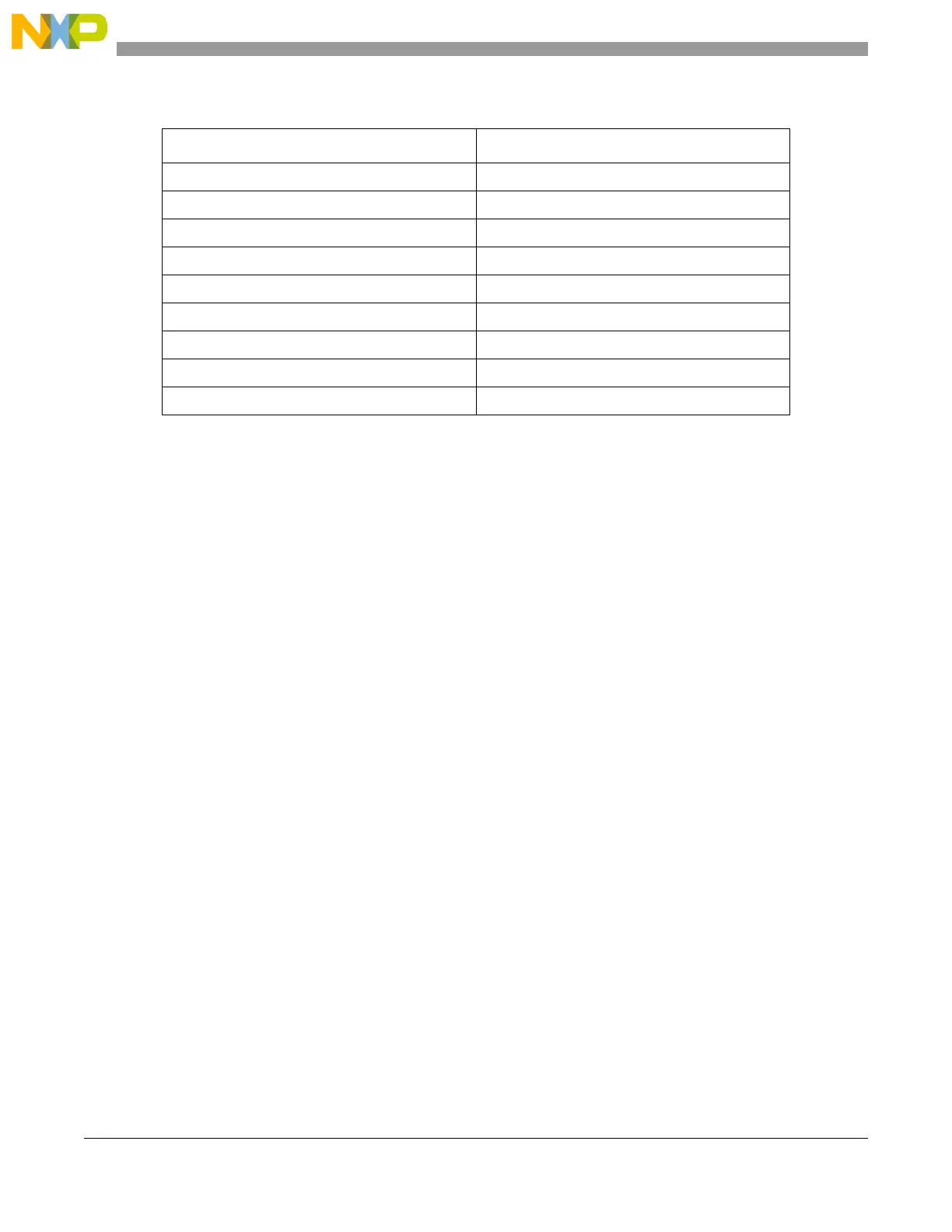

I2C 44

LINFlex_0 48

LINFlex_1 49

LINFlex_2 50

LINFlex_3 51

PIT 92

RTC/API 91

SIUL 68

WKPU 69

Table 8-16. Peripheral control registers by peripheral (continued)

Peripheral ME_PCTLn

Loading...

Loading...